www.ti.com

2.3.9.1

Translation for MMR space

A0

A0

A2

A2

A1

A1

A3

A3

L2 offset 0x0

DSP defined MMR

offset 0x1000

Byte

lane 0

31

Byte

lane 3

DMA 32b

0

2.3.9.2

Endian Conversion (TMS320TCI6482)

RapidIO defined bit positions

A0 A1 A2 A3

31

0

MMR offset 0x0000

B0 B1 B2 B3

MMR offset 0x0004

C0 C1 C2 C3

MMR offset 0x0008

D0 D1 D2 D3

MMR offset 0x000C

RapidIO

defined

MMR

offsets

A0A1A2A3B0B1B2B3 C0C1C2C3D0D1D2D3

Header fields

Type 8

Response

A0 A1 A2 A3

Byte

address 3

Byte

Byte

address 0

L2 offset 0x0

B0 B1 B2 B3

L2 offset 0x4

C0 C1 C2 C3

L2 offset 0x8

D0 D1 D2 D3

L2 offset 0xC

Big Endian

Little Endian

A3 A2 A1 A0

Byte

address 0

address 3

L2 offset 0x0

B3 B2 B1 B0

L2 offset 0x4

C3 C2 C1 C0

L2 offset 0x8

D3 D2 D1 D0

L2 offset 0xC

Double-word0

Double-word1

The desired operation is to send a Type 8 maintenance request to an external device.

The goal is to read 16B of RapidIO MMR

from an external device, starting offset 0x0000.

This operation involves the LSU block and utilizes the DMA for transferring the response

packet payload.

SRIO Functional Description

There are no Endian translation requirements for accessing the local MMR space. Regardless of the

device memory Endian configuration, all configuration bus accesses are performed on 32-bit values at a

fixed address position. The bit positions in the 32-bit word are defined by this specification. This means

that a memory image which will be copied to a MMR is identical between Little Endian and Big Endian

configurations. Configuration bus reads are performed in the same manner.

Figure 30

illustrates the

concept. The desired operation is to locally update a serial RapidIO MMR (offset 1000h) with a value of

A0A1A2A3h, using the configuration bus.

Figure 30. Configuration Bus Example

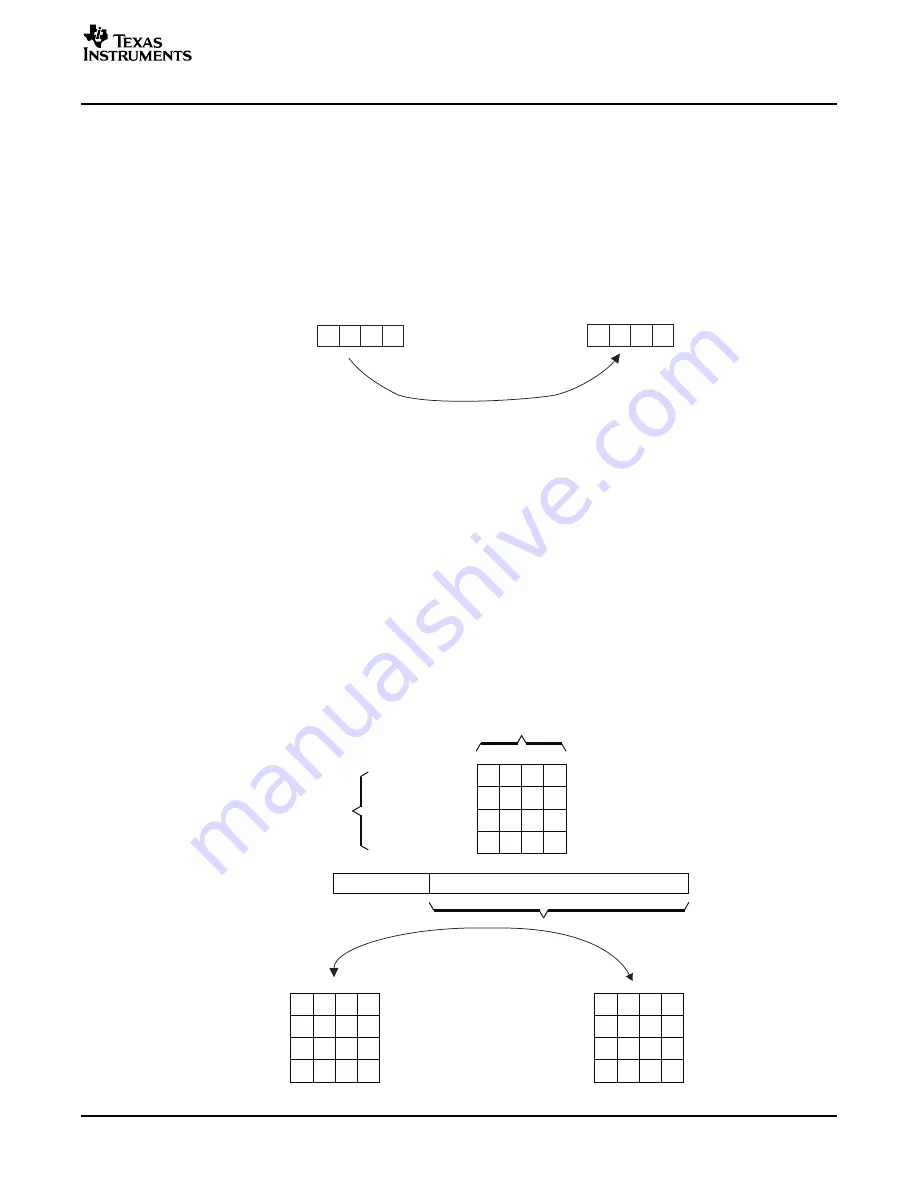

When accessing RapidIO defined MMR within an external device, RapidIO allows 4 bytes, 8 bytes, or any

multiple of a double-word access (up to 64 bytes) for type 8 (maintenance) packets. The peripheral only

supports 4-byte accesses as the target, but can generate all sizes of request packets. RapidIO is defined

as Big Endian only, and has double-word aligned Big Endian packet payloads.

The DMA, however, supports byte wide accesses. The peripheral performs Endian conversion on the

payload if Little Endian is used on the device. This conversion is not only applicable for type 8 packets, but

is also relevant for all outgoing payloads of NWRITE, NWRITE_R, SWRITE, NREAD, and message

packets. This means that the memory image is different between Little Endian and Big Endian

configurations, as shown in

Figure 31

.

Figure 31. DMA Example

SPRUE13A – September 2006

Serial RapidIO (SRIO)

69

Submit Documentation Feedback