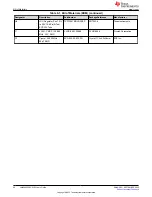

Table 6-1. Description of Evaluation Board Inputs and Outputs (continued)

CONNECTOR NAME

SIGNAL TYPE, INPUT/OUTPUT

DESCRIPTION

Power

VccEXT(J39/J40/TP13)

Vcc(TP12)

Power, Input

Main power supply input for the evaluation board.

The LMK04832SEPEVM default is setup to use the

voltage regulator. This is a space grade (SEP) voltage regulator.

0-Ω resistors R93, R94 and R95 can be re-configured to route

power through the onboard commercial grade LDO, the

. The LMK04832-SEP contains internal voltage regulators for

the VCO and other internal blocks. The clock outputs do not have

an internal regulator, so a clean power supply with sufficient output

current capability is required for optimal performance. If using an

external voltage please ensure the voltage is filtered to get the best

performance on the outputs.

Apply power to either Vcc SMA(J39) or terminal block(J40), but not

both.

Clock Inputs

CLKin0_P(J32),

CLKin0_N(J31),

CLKin1_P(J34),

CLKin1_N(J33)

OSCout_P(J29),

OSCout_N(J30)

Fin0_P(J37),

Fin0_N(J38)

Analog, Input

Reference Clock Inputs for PLL1 or PLL1 (CLKin0, CLKin1, CLKin2)

CLKin1_N is configured by default for a single-ended reference clock

input from a 50-Ω source. The non-driven input pin CLKin1_P can be

configured as R15 - DNI and R216 replace with 0-Ω resistor. CLKin0

is configured by default for a differential reference clock input from a

50-Ω source.

CLKin1 is the default reference clock input selected in the TICS Pro.

If OSCout is to be used as a CLKin2, then the PCB must be updated

to operate as an input instead of an output.

Clock Distribution with Fin0 or CLKin1/Fin1

Fin0 and CLKin1 (Fin1) are shared for use as an RF Input for Clock

Distribution mode or for an external VCO mode.

External Feedback Input (FBCLKin) for 0-Delay

CLKin1 is shared for use as an external feedback clock input

(FBCLKin) to PLL1 N or PLL2 N for 0-delay mode. Refer to the

LMK04832-SEP (

) data sheet for more details on using

0-delay mode with the evaluation board and the evaluation board

software.

OSCin,

PLL2 reference/PLL1 feedback

OSCin_P(J36),

OSCin_N(J35)

Analog, Input

Feedback VCXO clock input to PLL1 and Reference clock input to

PLL2.

The single-ended output of the onboard VCXO (Y1/Y2) drives the

OSCin_N input of the device and the OSCin_P input of the device is

connected to GND with 0.1 µF. VCXO Y1 and Y2 may also be used

with differential VCXOs.

An external VCXO may be optionally attached through these SMA

connectors with minor modification to the components going to the

OSCin pins of device.

A single-ended or differential signal may be used to drive the OSCin

pins and must be AC coupled. If operated in single-ended mode, the

unused input must be connected to GND with 0.1 µF.

Refer to the LMK04832-SEP (

) data sheet

Electrical

Characteristics

table for PLL2 Reference Input (OSCin)

specifications.

VCO Tuning Voltages

VTUNE1 (TP1/J41)

VTUNE2 (TP2/J42)

Analog, Input/Output

Tuning voltage output from the loop filter for PLL1 and PLL2 of the

LMK04832-SEP. If an external VCXO is used, this tuning voltage can

be connected to the voltage control pin of the external VCXO.

The default board does not come with J41 and J42 populated.

Evaluation Board Inputs and Outputs

10

LMK04832SEPEVM User’s Guide

Copyright © 2022 Texas Instruments Incorporated