MTLC User Manual

21

May 22, 2014

section

3.5 Using Terasic Multi-Touch IP

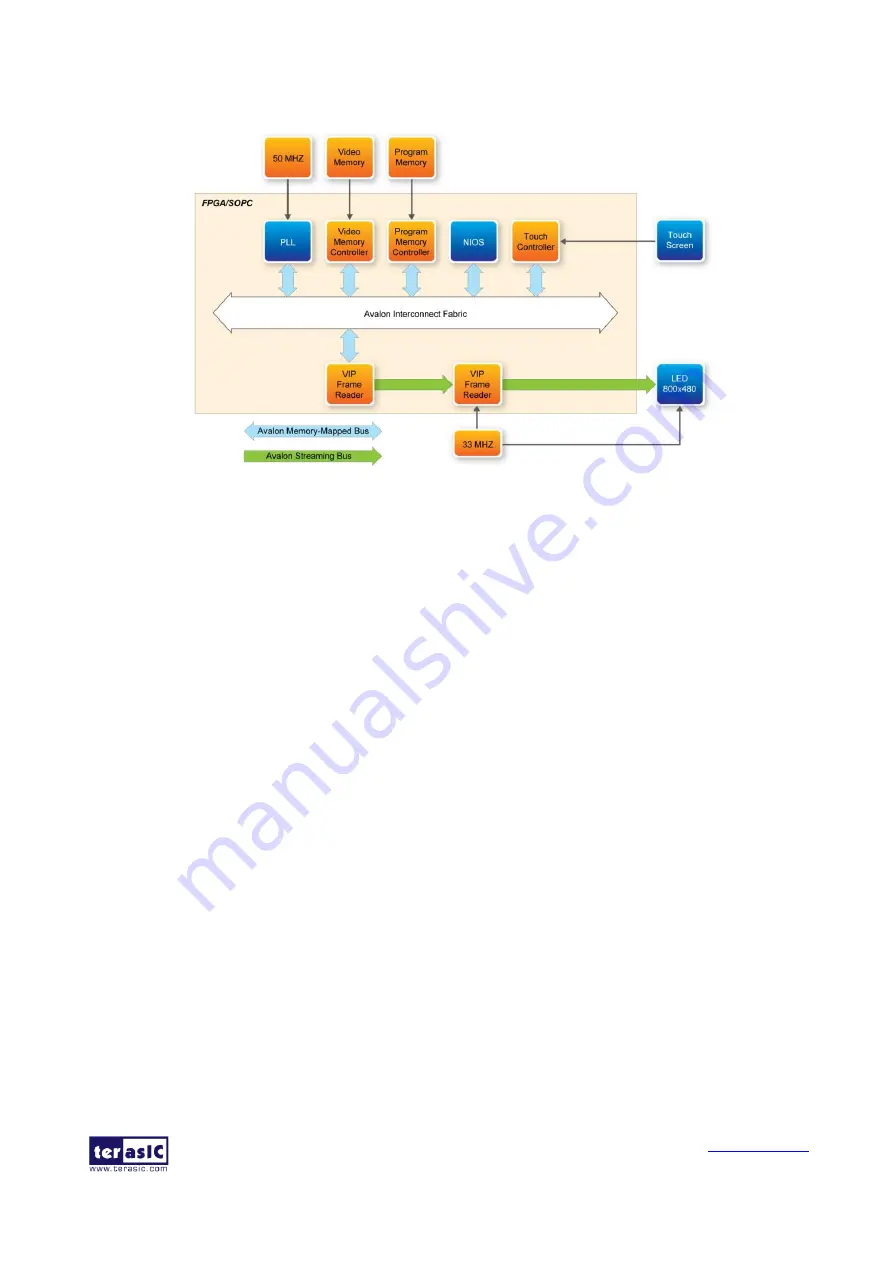

Figure 4-1 Block Diagram of the Painter Demonstration

Demonstration Source Code

Project directory: Painter

Bit stream used: Painter.sof

Nios II Workspace: Painter \Software

Demonstration Batch File

Demo Batch File Folder: Painter \demo_batch

The demo batch file includes the following files:

Batch File: test.bat, test_bashrc

FPGA Configuration File: Painter.sof

Nios II Program: Painter.elf

Demonstration Setup

1.

Make sure Quartus II and Nios II are installed on your PC

2.

Power on the DE2-115 board

3.

Connect USB-Blaster to the DE2-115 board and install USB-Blaster driver if necessary

4.

Execute the demo batch file “test.bat” under the batch file folder, Painter \demo_batch

5.

After Nios II program is downloaded and executed successfully, you will see a painter GUI in

the LCD.

shows the GUI of the Painter Demo.

The GUI is classified into three areas: Palette, Canvas, and Gesture. Users can select pen color

from the color palette and start painting in the Canvas area. If gesture is detected, the

associated gesture symbol is shown in the gesture area. To clear canvas content, press the

Summary of Contents for MTLC

Page 1: ...1 ...