Applications—

7A42

APPLICATION

3

ADDING EDGE SENSITIVITY

TO

YOUR

TRIGGER FUNCTION

When

developing

a

microprocessor

based

system,

it

is

important

to

ensure

that

data

being

“read"

from or “

written"

into

memory

remains

stable

at

specified

times.

The

7A42 Logic

Triggered Vertical

Amplifier

can

monitor these

data

lines

and

trigger

on

an

error

condition by

means

of

its

level

and

edge

sensitive

Trigger

Function

features.

In

addition

to

recognizing

logic

high

and low

levels, the

7A42

can

incorporate

one

edge

sensitive

channel

into

each

product (AND

function).

Because each

Trigger

Function

(A

or

B)

can

contain

two

products,

two

independent

Edge

operators

per

Trigger

Function

are

available.

Edge-sensitive

triggering

can

monitor

data

lines

and check

to

ensure

that

the

data

remains

stable.

MEASUREMENT

TECHNIQUE

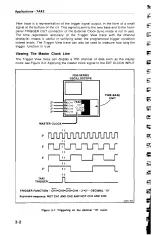

Figure

3-5

illustrates

the

timing

requirements

of

a

typical

microprocessor

read

cycle.

The

Data

bus

may

change

states

during

the

first

200

nanoseconds

of

the

cycle

but

must

remain

stable

during

the final

100

nanoseconds

while

the

Figure

3-5.

Timing diagram of a typical

microprocessor read cycle.

3-

6