AN2339

Development and debugging tool support

15/20

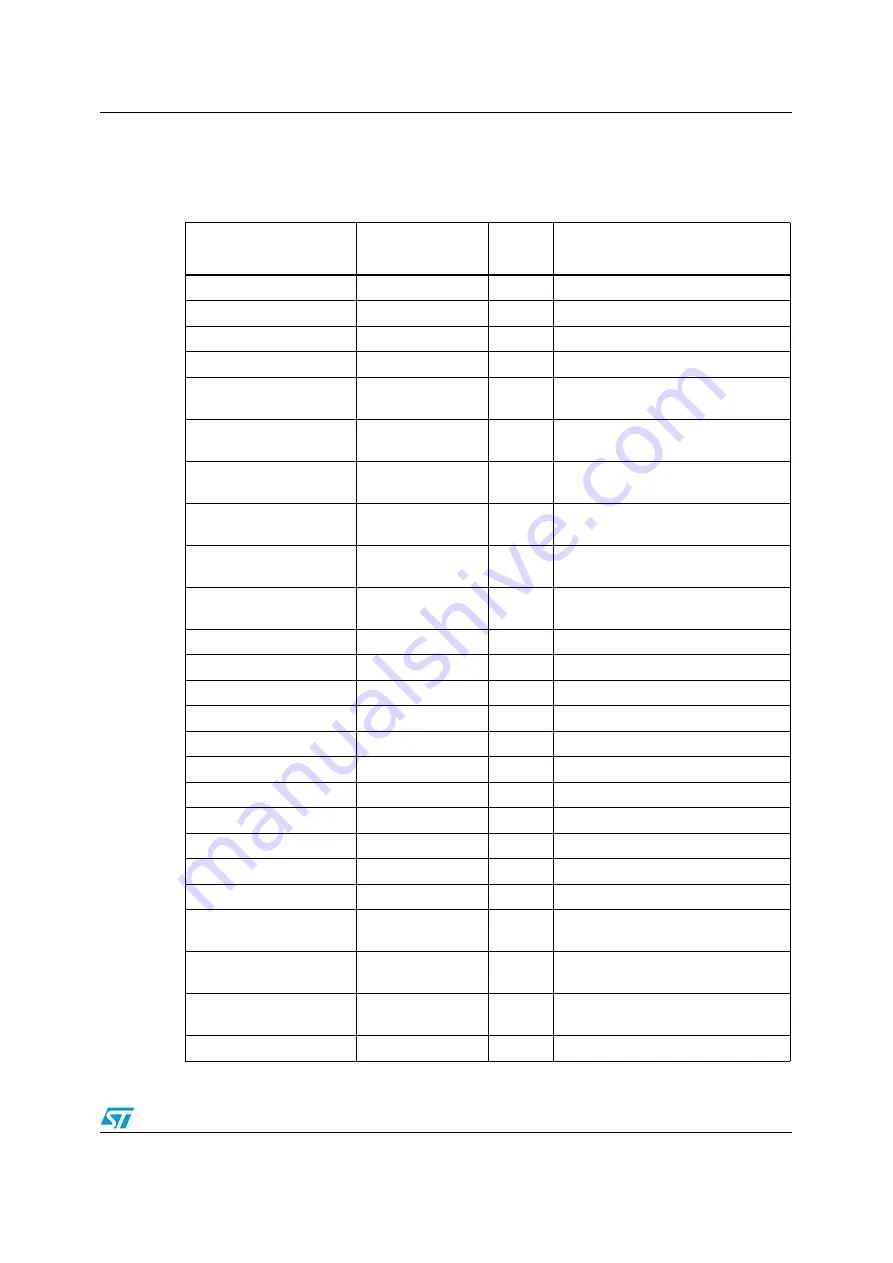

5.2.1 ETM

Interface

pins

The ETM interface pins consist of the following signals:

Table 3.

ETM interface signals

Target board

STR91x

name

Signal

pin

Description

NC

Not used

1

No Connect

NC

Not used

3

No Connect

VSSQ

VSSQ

5

Signal ground

DBGRQ Not

used

7

Debug

request

NSRST nRSTIN

9

Open-collector output from the run

control to the target system reset.

TDO

JTDO

11

Open-collector output from the run

control to the target system reset

RTCK

JRTCK

13

Return test clock from the target JTAG

port

TCK

JTCK

15

Test clock to the run control unit from

the JTAG port

TMS

JTMS

17

Test mode select from run control to

the JTAG port

TDI

JTDI

19

Test data input from run control to the

JTAG port

NTRST

JNTRST

21

Active-low JTAG reset

Port A TRACEPKT[15]

Not used

23

The trace packet port

Port A TRACEPKT[14]

Not used

25

The trace packet port

Port A TRACEPKT[13]

Not used

27

The trace packet port

Port A TRACEPKT[12]

Not used

29

The trace packet port

Port A TRACEPKT[11]

Not used

31

The trace packet port

Port A TRACEPKT[10]

Not used

33

The trace packet port

Port A TRACEPKT[9]

Not used

35

The trace packet port

Port A TRACEPKT[8]

Not used

37

The trace packet port

NC

Not used

2

No Connect

NC

Not used

4

No Connect

Port A TRACECLK

ETM_TRCLK

6

Clocks trace data on rising edge or

both edges

DBGACK

Not used

8

Debug acknowledge from the test

chip, high

when in debug state

EXTRIG

ETM_EXTRIG

10

Optional external trigger signal to the

Embedded trace Macrocell (ETM)

VTRef

VDDQ

12

Signal level reference