Hardware layout and configuration

UM2198

22/69

DocID030511 Rev 1

8.14 FD-CAN

The STM32H743I-EVAL Evaluation board supports one channel of the Flexible Data Rate

CAN (FD-CAN) communication bus, based on the 3.3 V CAN transceiver.

The standby signal on the FD-CAN transceiver is controlled by PD3 of the STM32H743XI.

Other FD-CAN signals are shared with USB OTG1 FS signals.

8.15 Ethernet

The STM32H743I-EVAL Evaluation board supports 10M/100M Ethernet communication by

a PHY LAN8742A (U5) and integrated RJ45 connector (CN1). Ethernet PHY is connected

to STM32H743XI through the RMII interface.

A 50-M reference clock can be generated by PHY with 25-M crystal or with 25-M MCO from

STM32H743XI. These two resources can be selected by setting

jumper JP5 as shown in

Table 12

.

8.16 Memories

An 8M x 32-bit SDRAM is connected to the SDRAM bank1 of the FMC interface of the

STM32H743XI microcontroller.

A 1Mx16-bit SRAM is connected to the NOR/PSRAM2 bank1 of the FMC interface and both

8-bit and 16-bit accesses are allowed by BLN0 and BLN1, connected to BLE and BHE of

SRAM respectively.

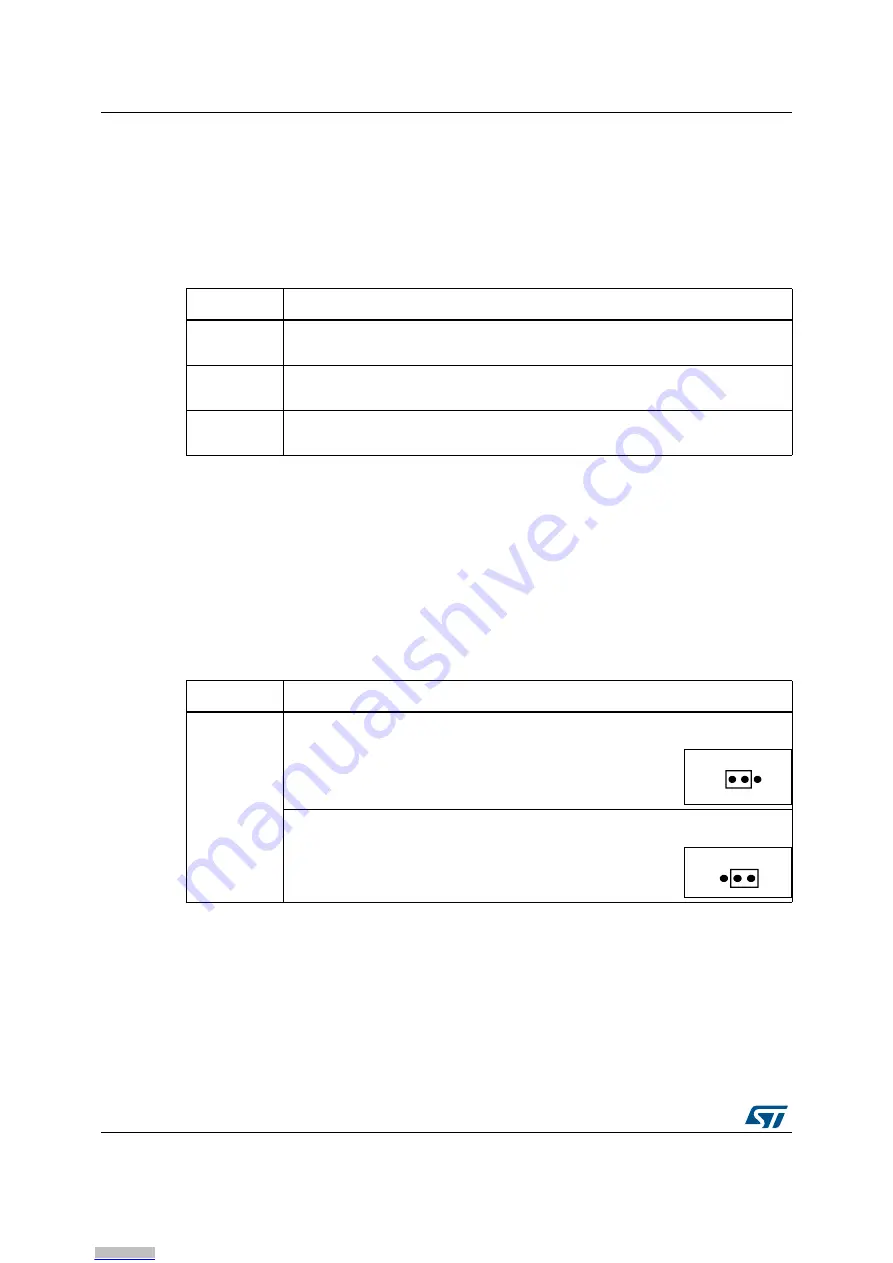

Table 11. CAN related jumpers and solder bridges

Jumper

Description

JP1

CAN terminal resistor is enabled when JP1 is fitted.

Default setting: Not fitted

JP2

PA12 is connected with FDCAN TX signal when JP2 is fitted.

Default setting: Not fitted

SB50

PA11 is connected with FDCAN RX signal when SB50 is closed.

Default setting: Open

Table 12. Ethernet related jumpers

Jumper

Description

JP5

50M RMII reference clock is generated by an external crystal X3 when JP5 is set as

shown to the right: (Default setting)

50M RMII reference clock is generated by MCO at PA8 when JP5 is set as shown to

the right:

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from

Downloaded from