STR-DN1010

STR-DN1010

19

19

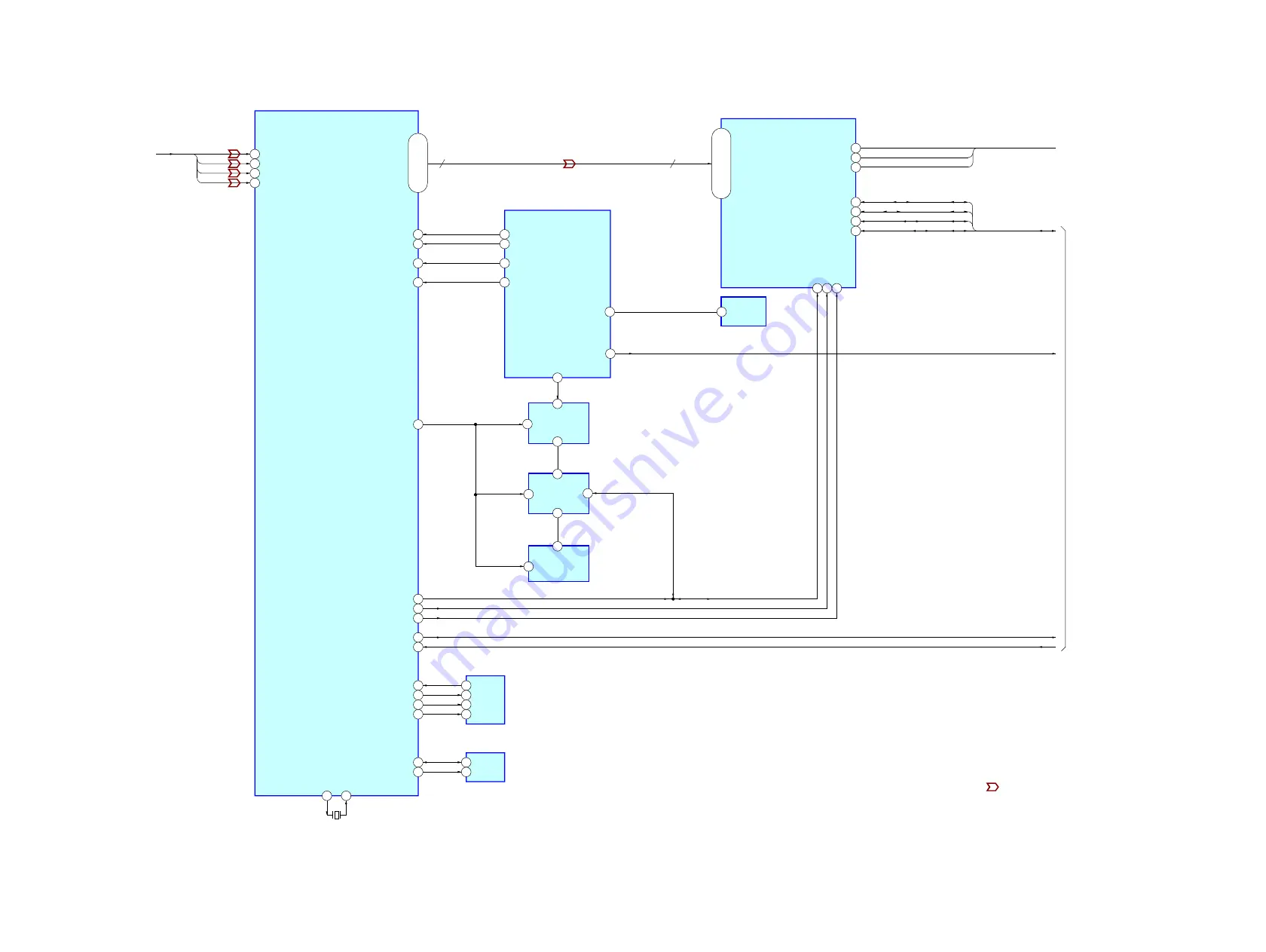

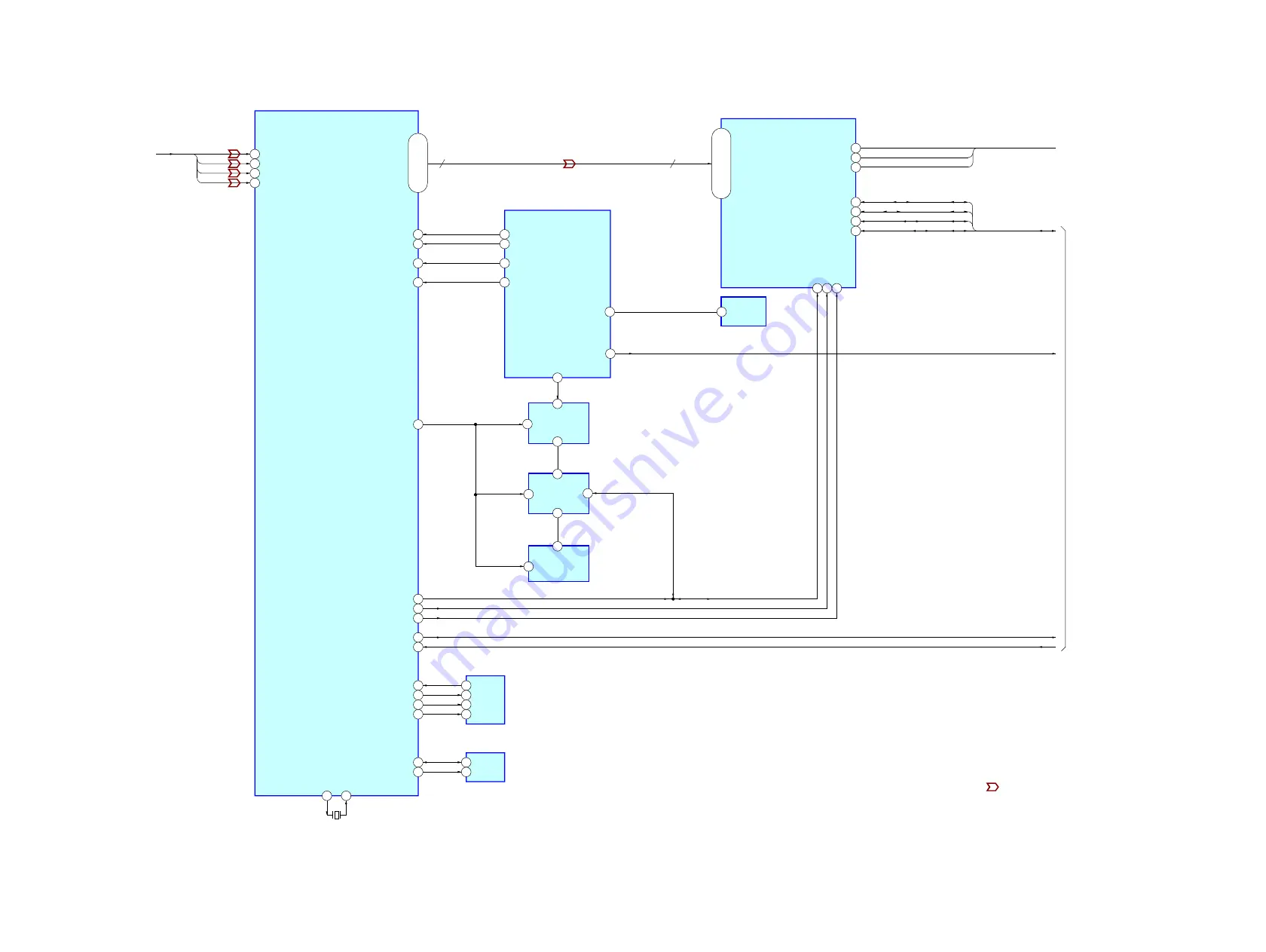

5-3. BLOCK DIAGRAM - VIDEO Section -

HSYNC_SEL/N1

22

UPDATE SW/N1 9

SYSTEM CONTROLLER

IC2018 (2/5)

VIDEO CONTROLLER

IC3201

DVS/VOP_VS 69

DHS/VOP_HS 68

HOST_SDATA/UART_DO/JTAG_MODE 23

HOST_SCLK/UART_DI/JTAG_CLK 22

ROM_SDI/ROM_WEn 109

ROM_SDO/A16/OPM2 108

ROM_SCLK/A17 107

ROM_SCSn/ROM_CSn 106

VIDEO DEINTERLACING

IC3202

INPUTCB[0], INPUTCB[1],

INPUTCB[2], INPUTCB[3],

INPUTCB[4], INPUTCB[5]

INPUTCB[6], INPUTCB[7]

INPUTY[0], INPUTY[1],

INPUTY[2], INPUTY[3],

INPUTY[4], INPUTY[5],

INPUTY[6], INPUTY[7],

INPUTCR[0], INPUTCR[1],

INPUTCR[2], INPUTCR[3],

INPUTCR[4], INPUTCR[5],

INPUTCR[6], INPUTCR[7],

B1P

221

C1P

223

A1P

219

A4P

249

CY, CB,

CR, CVBS

CR

CVBS

CY

CB

71, 72, 75 – 80, 85 – 89,

92 – 94, 103 – 1

10

24

24

FLI_DATA/N1

6

FLI_CLK/N1

7

HSYNC_SEL/N1

FLI STBY/N1

22

GPIO 0

24

10

GPIO10/SIPC_SDATA/A20

PD23/B7/GPIO48 – PD20/B4/GPIO45,

CHON_LV_O/B3, CH0P_LV_O/B2,

CH1N_LV_O/B1, CH1P_LV_O/B0,

CH2N_LV_O/G7, CH2P_LV_O/G6,

CLKN_LV_O/G5, CLKP_LV_O/G4,

CH3N_LV_O/G3, CH3P_LV_O/G2,

CH0N_LV_E/G1, CH0P_LV_E/G0,

CH1N_LV_E/R7, CH1P_LV_E/R6,

CH2N_LV_E/R5, CH2P_LV_E/R4,

CLKN_LV_E/R3, CLKP_LV_E/R2,

CH3N_LV_E/R1, CH3P_LV_E/R0

42

GPIO9/SIPC_SCLK/A19 41

RESETn 8

GPIO34 156

HSN 31

VSN 32

VOUTCLK

INPUTVCLK

INPUTVSN

INPUTDE

55

SCL 62

RESETN 63

SDA 61

DE 35

60 68 66

HSYNC SELECT

IC3205

A

Ch0

Ch1

+1.8 REG

IC3210 (1/2)

DEN/VOP_FLD 67

DCLK/VOP_CLK 70

DCK, HSYNC,

VSYNC,DE

SDA, SCL, ABT_RST

UPDATE_SW

OCM_UDO_0

OCM_UDI_0

DE

HSYNC

VSYNC

DCK

SDA

SCL

ABT_RST

X3201

19.6608MHz

XTAL

12

TCLK

13

SERIAL FLASH

IC3207

SCK

6

SO

2

SI

5

CE#

1

MSTR_SDATA 29

MSTR_SCLK 28

EEPROM

IC3208

SDA

5

SCL

6

102 – 99, 96 – 87,

84 – 75

W

MAIN SECTION

(Page 17)

V

DIGITAL VIDEO

SECTION

(Page 18)

D

DIGITAL VIDEO

SECTION

(Page 18)

6LJQDOSDWK

: VIDEO

5

&RQW

6

3

HSYNC SELECT

IC3206

1PR

2Q

1CK

1D

4

1

9

2

HSYNC SELECT

IC3204

3

INA

INB

2

1