3-5

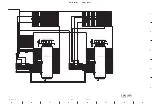

HXC-100/V2 (J, E)

3-5

2

3

4

5

1

A B

C

D

E

F

G

H

CD-61 (3/12)

CD-61 (3/12)

GND

MST-74CK_in

002

47

RB312

1

2

3

4

5

6

7

8

220

RB305

1

2

3

4

5

6

7

8

+3.2V

0

R303

TP301

0.1uF

C303

100k

R338

22

R307

FB302

GND

CDCVF2510APWR

IC301

AGND

1

VCC1

2

1Y0

3

1Y1

4

1Y2

5

GND1

6

GND2

7

1Y3

8

1Y4

9

VCC2

10

G

11

FBOUT

12

FBIN

13

VCC3

14

1Y5

15

1Y6

16

1Y7

17

GND3

18

GND4

19

1Y8

20

1Y9

21

VCC4

22

AVCC

23

CLK

24

+3.2V

0.1uF

C306

10

R327

+3.2V

GND

100k

RB303

12

34

56

78

+3.2V

+3.2V

GND

22

R309

CPU_I/F

TC7SZ08FU(TE85R)

(1/2)

IC306

2

1

4

10

R331

22

R313

FB301

GND

0.1uF

C302

CPU_BUS

002

47

RB311

1

2

3

4

5

6

7

8

0.1uF

C318

0.1uF

C304

220

RB308

1

2

3

4

5

6

7

8

MST-74CK_GND

002

0.1uF

C305

22

R312

220

RB309

1

2

3

4

5

6

7

8

GND

GND

10k

R329

GND

TC7SZ08FU(TE85R)

IC310 (2/2)

3

GND

5

VCC

22

R315

GND

+3.2V

GND

GND

470

R304

22

R302

CPU-CLK_DEMAP

010

CPU-CLK_DEMUX

007

2.2k

R305

+3.2V

FB303

2.2k

R328

1k

NM

R301

22

R308

NM

+3.2V

47

RB310

1

2

3

4

5

6

7

8

GND

+3.2V

22

R311

0.1uF

C309

0.1uF10V

C310

22

R306

10

R330

100k

RB307

12

34

56

78

220

RB306

1

2

3

4

5

6

7

8

+3.2V

10pF

NM

C301

47

RB313

1

2

3

4

5

6

7

8

22

R310

22

R314

C308

0.1uF

TC7SZ08FU(TE85R)

(2/2)

IC306

3

GND

5

VCC

0.1uF

C311

CPU-CK_in

002

CPU-CK_GND

002

xRESET_in

002

GND

0

R326

CD-RESET_2

010

CD-RESET_3

004,007

CD-RESET_4

008

CD-RESET_1

006

RESET-TX

002

TC74VHC245FT(EKJ)

IC303

A1

2

A2

3

A3

4

A4

5

A5

6

A6

7

A7

8

A8

9

OE

19

DIR

1

GND

10

B8

11

B7

12

B6

13

B5

14

B4

15

B3

16

B2

17

B1

18

VCC

20

TC74VHC245FT(EKJ)

IC304

A1

2

A2

3

A3

4

A4

5

A5

6

A6

7

A7

8

A8

9

OE

19

DIR

1

GND

10

B8

11

B7

12

B6

13

B5

14

B4

15

B3

16

B2

17

B1

18

VCC

20

100k

RB317

12

34

56

78

100k

RB318

12

34

56

78

+3.2V

100k

RB302

12

34

56

78

100k

RB304

12

34

56

78

74M-CLK-FPGA-DEMAP

010

74M-CLK-DAYTONA-MAIN 004

74M-CLK-FPGA-DEMUX

007

74M-CLK-DPR-FF

008

74M-CLK-FPGA-DEMUX2 007

74M-CLK-DPR

002

TC74VHC138FT(EKJ)

IC305

A

1

B

2

C

3

G1

6

G2A

4

G2B

5

GND

8

Y7

7

Y6

9

Y5

10

Y4

11

Y3

12

Y2

13

Y1

14

Y0

15

VCC

16

TC7SZ08FU(TE85R)

IC310 (1/2)

2

1

4

R3112N281A-TR-FA

IC309

CD

5

GND

3

OUT

1

VDD

2

NC

4

+3.2V

GND

+3.2V

0.01uF

C316

GND

1uF

C315

NM

47k

R335

GND

0.01uF

C317

0.1uF

C314

0

R334

TC7SZ08FU(TE85R)

IC302 (1/2)

2

1

4

TC7SZ08FU(TE85R)

IC308 (1/2)

2

1

4

+3.2V

100k

R350

100k

R351

+3.2V

+3.2V

TC7SZ08FU(TE85R)

IC302 (2/2)

3

GND

5

VCC

0.1uF

C322

GND

+3.2V

TC7SZ08FU(TE85R)

IC308 (2/2)

3

GND

5

VCC

0.1uF

C323

GND

100

R352

0.8

CL300

0.8

CL301

CPU-D6

CPU-A1

CS0

CPU-A2

CPU-D3

CPU-A3

CS0

CPU-A0

CPU-D2

CPU-RD

CPU-D0

CPU-A4

CPU-A3

CS0_in

CPU-A2

ADDR(1)_in

BUS(4)_in

CPU-A4

BUS(7)_in

CPU-D7

ADDR(4)_in

ADDR(2)_in

BUS(0)_in

CS_DEMUX

ADDR(0)_in

BUS(2)_in

BUS(1)_in

BUS(3)_in

CPU-D4

CS_CAFE-T

ADDR(3)_in

BUS(5)_in

CS_TORINO

CPU-D5

CPU-D1

CS_DEMAP

BUS(6)_in

WR_in

RD_in

CPU-WR

CPU-RD

CPU-D7

CPU-D6

CPU-D5

CPU-D4

CPU-D3

CPU-D2

CPU-D1

CPU-D0

+3.2V

RESET

MST-74M

CLOCK

from/to DPR

(0.02uF-> 90mS)

from MB

CPU_I/F

4.49 x C(uF)[S]

MST 74MHz

to CAFE-T

to TORINO

to DAYTONA-MAIN-ENC

to DAYTONA-RET-DEC

DAYTONA MAIN ENC

DAYTONA RET DEC

CAFE-T

TORINO

FPGA(DEMUX)

FPGA(DEMAP)

+3.3V

FPGA(DEMAP)

FF to DPR

DAYTONA MAIN ENC

FPGA(DEMUX)

FPGA(DEMUX)

DPR

RET

DEMUX

FF

MAIN

DAYTONA

RET DEC

SYS CLK

CAFE-T

SYS CLK

DAYTONA

MAIN ENC

from

DPR

from

TX

(N-ch_Open_Drain_Output)

PLL

DEMUX

PLL

(side A)

(side B)

R341

R339

100

100

R340

R342

100

100

220

100

R336

R337

006,007,010

CD-61 (3/12)

BOARD NO. 1-879-612-11

HSC-300_CD-61_011_3

Summary of Contents for HXC-100

Page 1: ...HD COLOR CAMERA HXC 100 SERVICE MANUAL Volume 2 1st Edition ...

Page 6: ......

Page 8: ......

Page 97: ...2 1 HXC 100 V2 J E 2 1 Section 2 Block Diagrams ...

Page 100: ......

Page 104: ......

Page 108: ......

Page 116: ......

Page 130: ......

Page 148: ......

Page 154: ......

Page 170: ......

Page 178: ......

Page 184: ......

Page 205: ......