HCD-HDX500/HDX501W

37

37

HCD-HDX500/HDX501W

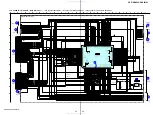

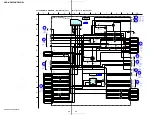

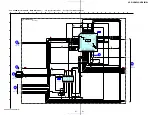

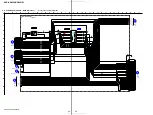

6-8. SCHEMATIC DIAGRAM – MAIN Board (3/13) –

•

See page 72 for IC Block Diagrams.

3.3

1.8

3.3

3.3

3.3

0

0

3.3

3.3

1.6

3.3

3.3

3.3

1.6

1.7

1.8

3.3

1.6

1.6

1.6

3.3

3.3

1.6

3.3

1.6

1.6

1.6

3.3

16V

47

C3031

0.1

C3040

0.1

C3039

0.1

C3038

0.1

C3037

0.1

C3036

0.1

C3035

0.1

C3034

0.1

C3033

0.1

C3032

R3502 100

R3501

100

100

R3402

100

R3401

100

R3302

100

R3301

R3076

47

R3075

47

100

R3073

100

R3072

100

R3071

100

R3070

100

R3069

100

R3068

100

R3067

R3037

47

R3035

47

R3034

47

470

R3032

470

R3031

1k

R3063

1k

R3064

10k

R3033

10k

R3059

10k

R3060

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

SHIFT

LAT1

LAT2

LAT3

DIAG

OVF1

OVF2

D-GND

AMP_D1

AMP_D2

AMP_D3

AMP_BCKO

AMP_LRCKO

AMP_MCKO

100p

C3069

100p

C3068

0

R3044

0

R3045

0

R3046

0.01

C3071

R3074

47

0

R3914

0

R3913

0

R3917

0

R3911

0

R3912

SWL-

SWL+

SWR-

C-

C+

DIAG

1000p

C3070

100p

C3067

P-GND

NSPMUTE

+3.3V

XFSOIN

FSOI

GND

FLAGL

AMP_LRCKO

AMP_BCKO

AMP_MCKO

AMP_D2

AMP_D1

+B

A

0

R4002

INIT

SOFTMUTE

PGMUTE

SC_DT

SCSHIFT

SCLATCH3

SC_DT

SCSHIFT

OVF

OVFFLAG2

INIT

SOFTMUTE

SCLATCH3

SCLATCH1

SCLATCH2

OVFFLAG2

(3/13)

MAIN BOARD

E

8

D

C

2

7

5

10

6

9

G

A

B

1

3

4

w w w . x i a o y u 1 6 3 . c o m

Q Q 3 7 6 3 1 5 1 5 0

9

9

2

8

9

4

2

9

8

T E L

1 3 9 4 2 2 9 6 5 1 3

9

9

2

8

9

4

2

9

8

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299