4-4

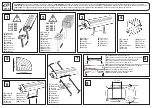

BKP-7934 IMM

IC

CXD8888R (SONY)

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

CURSOR GENERATOR

—TOP VIEW—

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

I

I

I

I

I

I

I

I

I

I

—

O

O

O

O

O

O

O

O

O

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

GND

C0

C1

C2

C3

C4

C5

C6

C7

C8

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

O

O

O

O

O

O

O

I

—

—

O

O

O

O

O

O

O

O

O

O

C9

C10

C11

C12

C13

C14

C15

TEST

GND

V

CC

TEG1

TEG2

TEG3

OD4

OD5

OD6

OD7

OD8

OD9

CURS

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

O

O

O

O

I

I

I

I

I

—

I

I

I

I

I

I

I

I

I

I

EXTG

TGLD

BMLD

EXLD

CCD

PBLK

VD

HD

CLK1

GND

CLK2

SCK

SDT

SLD

CNV

CNAB

A0

A1

A2

A3

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

I

I

I

I

I

I

I

I

I

I

—

—

I

I

I

I

I

I

I

I

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

GND

V

CC

A14

A15

B0

B1

B2

B3

B4

B5

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

INPUTS

A0 - A15

B0 - B15

CCD

CLK1, CLK2

CNAB

CNV

HD

PBLK

SCK

SDT

SLD

TEST

VD

OUTPUTS

BMLD

C0 - C15

CURS

EXLD

EXTG

OD4 - OD9

TEG1 - TEG3

TGLD

: A

: B

: CCD 40/50

: CLOCK

: OUTPUT SELECT A/B

: V CURSOR FIELD/ALL

: HD

: PRE BLANKING

: SERIAL CLOCK

: SERIAL DATA

: SERIAL LOAD

: TEST

: VD

: BLEMISH LOAD

: C

: CURSOR

: EXTERNAL LOAD

: DOT

: DATA

: TEST TRIGGER

: TG LOAD

EPM7128STC100-10 (ALTERA)

INPUTS

GCLK1, GCLK2

GCLR

OE1

,

OE2

: GLOBAL CLOCK1, 2

: GLOBAL CLEAR

: OUTPUT ENABLE1, 2

INPUT/OUTPUT

I/O : DATA

GCLK1

87

OE2

/GCLK2

90

OE1

88

GCLR

89

LAB A

I/O

CONTROL BLOCK

MACROCELLS

1 - 8

MACROCELLS

9 - 16

10

10

10

10

36

16

36

16

10

10

I/O

CONTROL BLOCK

LAB B

MACROCELLS

17 - 24

MACROCELLS

25 - 32

96 - 100,

92 - 94,

1 - 2

I/O

10

12 - 14,

4 - 10

I/O

10

10

10

PIA

10

10

36

16

10

LAB C

10

LAB D

10

36

16

10

19 - 25,

15 - 17

I/O

10

35 - 37,

27 - 33

I/O

10

36

16

10

LAB E

10

LAB F

10

36

16

10

44 - 50

40 - 42

I/O

10

60 - 62,

52 - 58

I/O

10

36

16

10

LAB G

LAB H

36

16

10

67 - 73,

63 - 65

I/O

*

ABOVE DIAGRAM SHOWS CONDITIONS BEFORE PROGRAMMING.

10

83 - 85,

75 - 81

I/O

10

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

V

CC

2

I/O

I/O

I/O

I/O

I/O

I/O

I/O

GND

I/O

I/O

I/O

I/O

I/O

I/O

V

CC

2

I/O

I/O

I/O

I/O

I/O

I/O

I/O

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

—

—

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

GND

I/O

I/O

I/O

I/O

I/O

I/O

I/O

V

CC

2

I/O

I/O

I/O

GND

V

CC

1

I/O

I/O

I/O

GND

I/O

I/O

I/O

I/O

I/O

I/O

I/O

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

V

CC

2

I/O

I/O

I/O

I/O

I/O

I/O

I/O

GND

I/O

I/O

I/O

I/O

I/O

I/O

V

CC

2

I/O

I/O

I/O

I/O

I/O

I/O

I/O

GND

I/O

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

—

I

I

I

I

—

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

V

CC

2

I/O

I/O

I/O

GND

GCLK1

OE1

GCLR

OE2

/GCLK2

V

CC

1

I/O

I/O

I/O

GND

I/O

I/O

I/O

I/O

I/O

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

76

80

85

90

95

100

FIELD PROGRAMMABLE LOGIC CIRCUIT

—TOP VIEW—

50

45

40

35

30

26

75

70

65

60

55

51

1

5

10

15

20

25

Summary of Contents for BKP-7934

Page 1: ...MSU UPGRADE UNIT BKP 7934 INSTALLATION AND MAINTENANCE MANUAL 1st Edition Revised 1 ...

Page 4: ......

Page 8: ......

Page 22: ......

Page 35: ...5 1 BKP 7934 IMM 5 1 Section 5 Block Diagrams ...

Page 40: ......

Page 41: ...6 1 BKP 7934 IMM 6 1 2 3 4 5 1 I J K L M N O P Section 6 Schematic Diagrams ...

Page 56: ......

Page 57: ...7 1 BKP 7934 IMM 7 1 Section 7 Board Layout ...

Page 62: ......