Copyright © Siemens AG 2010. All rights reserved.

Page

90

ERTEC 400 Manual

Technical data subject to change

Version 1.2.2

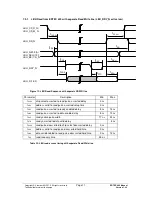

8.3 Address Assignment of PCI Register

The PCI registers are

32 bits in width

. The registers can be read or written to with 8-bit, 16-bit, or 32-bit

accesses.

PCI

(Base Address 0x8000_0000)

Offset Address

Byte 3

Byte 2

Byte 1

Byte 0

Access

Default

0x0000

Device_ID

Vendor_ID

R

0x4026110A

0x0004

Status

Command

R/W

0x02300000

0x0008

Class_Code

Revision_ID

R

0x000020A0

0x000C

BIST

Header_Type

Latency_Timer

Cache_Line_Size

R/W

0x00000000

0x0010

PCI_Base_Address_Register0

R/W

0x00000000

0x0014

PCI_Base_Address_Register1

R/W

0x00000000

0x0018

PCI_Base_Address_Register2

R/W

0x00000000

0x001C

PCI_Base_Address_Register3

R/W

0x00000000

0x0020

PCI_Base_Address_Register4

R/W

0x00000000

0x0024

PCI_Base_Address_Register5

R/W

0x00000000

0x0028

Cardbus_CIS_Pointer

R

0x00000000

0x002C

Subsystem_ID

Subsystem_Vendor_ID

R

0x00000000

0x0030

Expansion_ROM_Base_Address (Reserved)

R

0x00000000

0x0034

Reserved

Capability_Pointer

R

0x00000048

0x0038

Reserved

R

0x00000000

0x003C

Max_Lat

Min_Gnt

Interrupt_Pin

Interrupt_Line

R/W

0x00000000

0x0040

Device_ID

Vendor_ID

R/W

0x00000000

0x0044

Subsystem_ID

Subsystem_Vendor_ID

R/W

0x00000000

0x0048

PM_Capability

PM_next_item_ptr

PM_Capability_id

R

0x00020001

0x004C

PM_Data

PM_CSR_BSE

PM_Control_Status

R/W

0x00000000

0x0050

PCI_Base_Address_Mask_Register0

R/W

0x00000000

0x0054

PCI_Base_Address_Mask_Register1

R/W

0x00000000

0x0058

PCI_Base_Address_Mask_Register2

R/W

0x00000000

0x005C

PCI_Base_Address_Mask_Register3

R/W

0x00000000

0x0060

PCI_Base_Address_Mask_Register4

R/W

0x00000000

0x0064

PCI_Base_Address_Mask_Register5

R/W

0x00000000

0x0068

PCI_Base_Address_Translation_Register0

R/W

0x00000000

0x006C

PCI_Base_Address_Translation_Register1

R/W

0x00000000

0x007

PCI_Base_Address_Translation_Register2

R/W

0x00000000

0x0074

PCI_Base_Address_Translation_Register3

R/W

0x00000000

0x0078

PCI_Base_Address_Translation_Register4

R/W

0x00000000

0x007C

PCI_Base_Address_Translation_Register5

R/W

0x00000000

0x0080

Reserved

PCI_Arbiter_Config_Register

R/W

0x00000000

0x0084

Max_Lat

Min_Gnt

INT_Pin

Reserved

R/W

0x00000000

0x0088

PM_Capability

Reserved

R/W

0x00020000

0x008C

Class_Code

Revision_ID

R/W

0x00000000

0x0090

AHB_Base_Address_Register0

R/W

0x00000001

0x0094

AHB_Base_Address_Register1

R/W

0x00000000

0x0098

AHB_Base_Address_Register2

R/W

0x00000000

0x009C

AHB_Base_Address_Register3

R/W

0x00000000

0x00A0

AHB_Base_Address_Register4

R/W

0x00000000