SM-SX1/SX1W

– 42 –

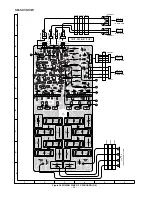

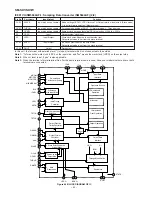

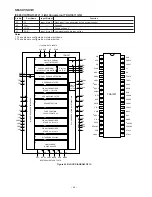

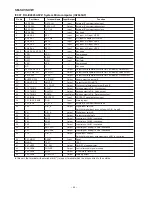

IC803 VHiTDA1307/-1: 1-Bit Conversion (TDA1307) (2/2)

39

CL

Input (Note 2)

Clock input, to be generated by the microprocessor

40

Vss

1

—

Ground 1

41

VDD3

—

Supply voltage 2

42

RAB

Input (Note 2)

Command/peak data request line

Pin No.

Port Name

Input/Output

Function

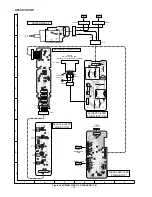

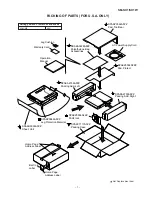

Figure 42 BLOCK DIAGRAM OF IC

1fs AUDIO DATA INPUTS

WS

SCK

SD

EFAB

1

2

3

4

TDA1307

MULTIPLE FORMAT

INPUT INTERFACE

ERROR CONCELMENT,

INTERPOLATION, MUTING

DIGITAL

OUTPUT

DIGITAL SILENCE DETECTION

DEEMPHASIS FILTER

FIR HALFBAND FILTER

STAGE 1: 1fs to 2fs

DC-CANCELING FILTER

PEAK DETECTION

FADE FUNCTION

VOLUME CONTROL

FIR HALFBAND FILTER

STAGE 2: 2 fs to 4 fs

FIR HALFBAND FILTER

STAGE 3: 4 fs to 8 fs

DITHER AND SCALING

3rd/4th ORDER

NOISE SHAPER

27

28

35

34

33

26

DOL

NDOL CDAC NDOR DOR

MODE

BITSTREAM DATA OUTPUTS

MICROPROCESSOR INTERFACE

DA 38

CL 39

RAB 42

POR 20

VDD3 8

VDD1 21

VDDOSC 24

VDDAL 29

VDDAR 32

VDD2 41

DSR 12

DSL 11

TEST1 36

TEST2 37

19 RESYNC

10 DOBM

13 DSTB

5 SBCL

6 SBDA

CRYSTAL

OSCIL-

LATOR

25 VSSOSC

22 XTAL1

23 XTAL2

15 CMIC

7 CDEC

14 CLC1

17 CLC2

18 CDCC

9 VSS2

16 VSS3

30 VSSAL

31 VSSAR

40 VSS1

CLOCK GENERATION & DISTRIBUTION

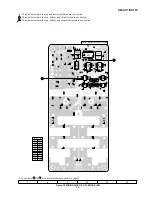

WS

SCK

SD

EFAB

SBCL

SBDA

CDEC

VDDC3

VSSC2

DOBM

DSL

DSR

DSTB

CLC1

CMIC

VSSC3

CLC2

CDCC

RESYNC

POR

VDDC1

RAB

VDDC2

VSSC1

CL

DA

TEST2

TEST1

CDAC

NDOR

DOR

VDDAR

VSSAR

VSSAL

VDDAL

NDOL

DOL

MODE

VSSOSC

VDDOSC

XTAL2

XTAL1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

TDA1307

Notes

1. These pins are configured as internal pull-down.

2. These pins are configured as internal pull-up.