Chapter 4 – SD Card Protocol Description

Revision 2.2

SanDisk SD Card Product Manual

© 2004 SanDisk Corporation

4-43

12/08/04

Data Transfer Mode

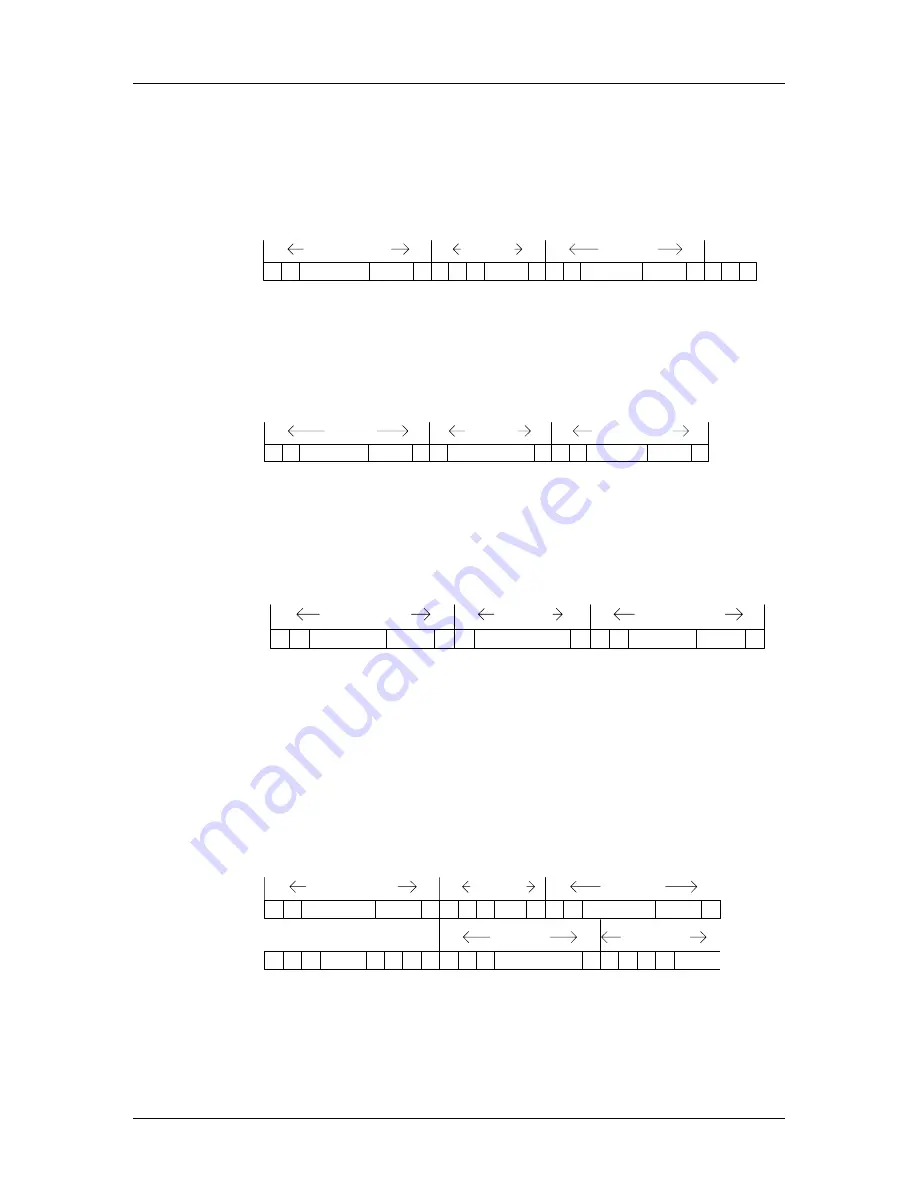

There is just one Z bit period followed by P bits pushed up by the responding card. This

timing diagram is relevant for all responded host commands except CMD1, 2, 3.

Command Response Timing (Data Transfer Mode)

Last Card Response

—Next Host Command Timing

After receiving the last card response, the host can start the next command transmission

after at least N

RC

clock cycles. This timing is relevant for any host command.

Timing Response End to Next CMD Start (Data Transfer Mode)

Last Host Command

—Next Host Command Timing

After the last command has been sent, the host can continue sending the next command

after at least N

CC

clock periods.

Timing of Command Sequences (All modes)

4.11 Data

Read

Single Block Read

The host selects one card for data read operation by CMD7 and sets the valid block length

for block-oriented data transfer by CMD16. The basic bus timing for a read operation is

shown in the

Transfer of Single Block Read

timing diagram. The sequence starts with a

single block read command, CMD17 that specifies the start address in the argument field.

The response is sent on the CMD line as usual.

Transfer of Single Block Read

Data transmission from the card starts after the access time delay N

AC

beginning from the

end bit of the read command. After the last data bit, the CRC check bits are suffixed to

allow the host to check for transmission errors.

CMD S T

Content

E Z

******

Z S T

Z

Host Command

N

CC

CRC

Host Command

Cycles

Content

CRC

E

CMD S T

Content

E Z

***

P S T

CRC

Response

Cycles

Content

CRC

E

Z P

DAT Z Z

****

Z Z

**********

Z

P S D

N

AC

Read Data

Cycles

D

Z

Z Z Z

P

D

***

CMD S T

Content

E Z

***

P S T

Z

Z Z

Host Command

N

CR

CRC

Response

Cycles

Content

CRC

Z

E

Z P

CMD S T

Content

E Z

******

Z S T

Z

Response

N

RC

CRC

Host Command

Cycles

Content

CRC

E