SAMSUNG Proprietary-Contents may change without notice

This Document can not be used without Samsung's authorization

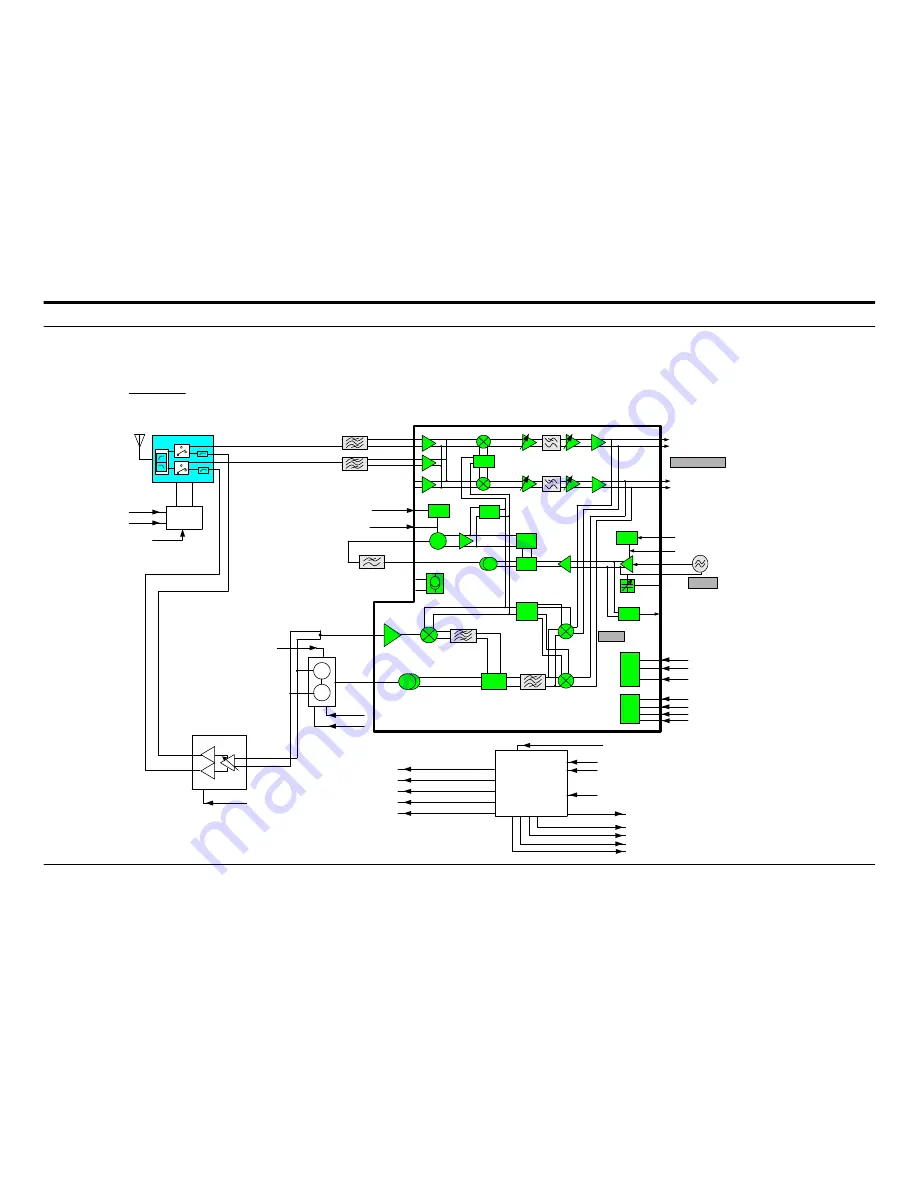

5. SGH-E820 Block Diagrams

5-1

1. RF Solution Block Diagram

100 kHz+fmod

REFIN

VC-TCXO

GSM

DCS/PCS

I+

fmod

I-

Q+

Q-

~

~

VAPC

FUJITSU EGSM RX SAW Filter

FAR-F5EB-942M50-B28CH (2.0X1.4)

IL=1.5dB typ 2.1dB max

Ripple=0.6dB typ 1.2dB max

Vcc_RF_VCO

Discrete

3

rd

Order

Loop Filter

fc = ? kHz

? ㉥? ? ?TX VCO

VOG1810F27KRA (5.7X5.0X1.5)

GSM =

880 ~ 915MHz

(Vt=0.5V ~ 3.0V )

kV = 55+-11 MHz/V Typ

DCS =

1710 ~ 1785MHz

(Vt=0.5V ~ 3.0V )

kV = 115+-23 MHz/V Typ

Pout= 6.5+-3 dBm typ.,Ic <= 30mA

Harmonics <= -10dBc

Micro Devices Quadband PAM

RF3146 (7 X 7)

GSM: Pout = 35.0 dBm E

ff

= 60%

DCS: Pout= 33.0 dBm E

ff

= 55%

RXON

Vcc_Tx_BURST

VBAT

HITACHI METAL ANT S/W

ESHS-C090T

Imax = 8 mA

Freq (MHz) Loss

880 - 915 1.28 dB

925 - 960 0.8 dB

1710 -1785 1.6 dB

1805 -1880 0.97 dB

Atten 2xfo : 43dB,26dB(GSM,DCS)

3xfo : 40dB,20dB(GSM,DCS)

EN

CLK

DATA

DCS S/W

OFFSET Mixer input power

-16dBm max, -22dBm min

f

compRF

=26MHz

Philips Transceiver

UAA3536

Pins IA,IB,QA and QB

V

IQ

: 1.25V

typ

. , 1.15V

min

, 1.35V

max

V

mod

: 0.5V

pp

QUAD

DIV

PFD

CP

VREG

~

Vcc_RF_LO

FracN

DIV

1:1/

2

VREG

26MHz

Vcc_REF(2.4V typ.)

Vcc_SYN

FESW1

FESW2

3W

BUS

CTL

REG

PWR

EN

GSM/DCS/PCS

DIV

QUAD

PFD

CP

f

TXIF

60/114MHz

+ I OUT

-

-

+

FESWON

SYNON

TXON

GSM S/W

PMU

HVS

VDD1

(1.35V min 2.95V max , 150mA )

VBat

(3.6V typ 3.0V min)

V_MODE

RF1_VDD

RF2_VDD

RF1_VDDS

RF2_VDDS

VDD2

(1.35V min 3.45V max , 150mA )

VDD3

(1.35V min 3.45V max , 100mA )

VDD4

(1.35V min 3.45V max , 150mA )

AVDD

(1.35V min 2.65V max , 100mA )

VCC_RX_TX

(2.7V ,100mA )

VCC_SYN

(2.7V , 100mA )

VCC_RF_VCO

(2.7V , 100mA )

VCC_CP

(4.0V , 25mA )

VCC_TX_BURST

(2.7V , 100mA )

PON_SYNT

PON_TX

PANASONIC DCS RX SAW Filter

EFCH1842TCA7 (2.0X1.4)

IL=1.8dB typ 2.5dB max

Ripple=0.6dB typ 1.5dB max

EGSM_MODE_SW

VCC_RX_TX

Vc_EGSM

DCS_MODE_SW

Vc_DCS

Inverter circuits

I OUT

Q OUT

Q OUT