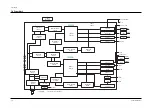

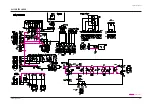

Block Diagram

7-6

Samsung Electronics

7-6 Tridimensional Y/C Module

SYNC

Separation

Bust-Lock

Clock

Generator

m

PC1862

m

PD6488

m

PD42280

TMS4C1060BDJ

A/D

8bit

D/A

9bit

D/A

9bit

3-Dimensional

Y/C Separation

Y Noise Reduce

Vertical peaking

2 Mbit(8x256K)

Field Memory

1 Mbit(4x256K)

Field Memory

DATA

CLOCK

L.P.F

6MHz

B.P.F

3.58MHz

L.P.F

6MHz

5V

Regulator

3.3V

Regulator

Amp.

Amp.

Amp.

Memory Control

Data In/Out

Memory Control

Data In/Out

VIDEO IN

9V

C OUT

2Vp-p

2Vp-p

Y OUT

Summary of Contents for HCH551WX

Page 2: ...ELECTRONICS Samsung Electronics Co Ltd NOV 1998 Printed in Korea 3APT52A 5501 ...

Page 23: ...MEMO 3 16 Samsung Electronics ...

Page 62: ...8 2 Samsung Electronics MEMO ...

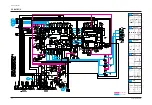

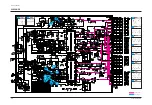

Page 67: ...Schematic Diagrams Samsung Electronics 9 5 9 5 3DCOMB1 Power Line Signal Line ...

Page 68: ...Schematic Diagrams 9 6 Samsung Electronics 9 6 IF_MODULE Power Line Signal Line ...

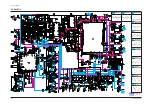

Page 73: ...Schematic Diagrams Samsung Electronics 9 11 9 11 CONTROL SUB Power Line ...