MEMORY MAP

KS57C2308/P2308/C2316/P2316

4-24

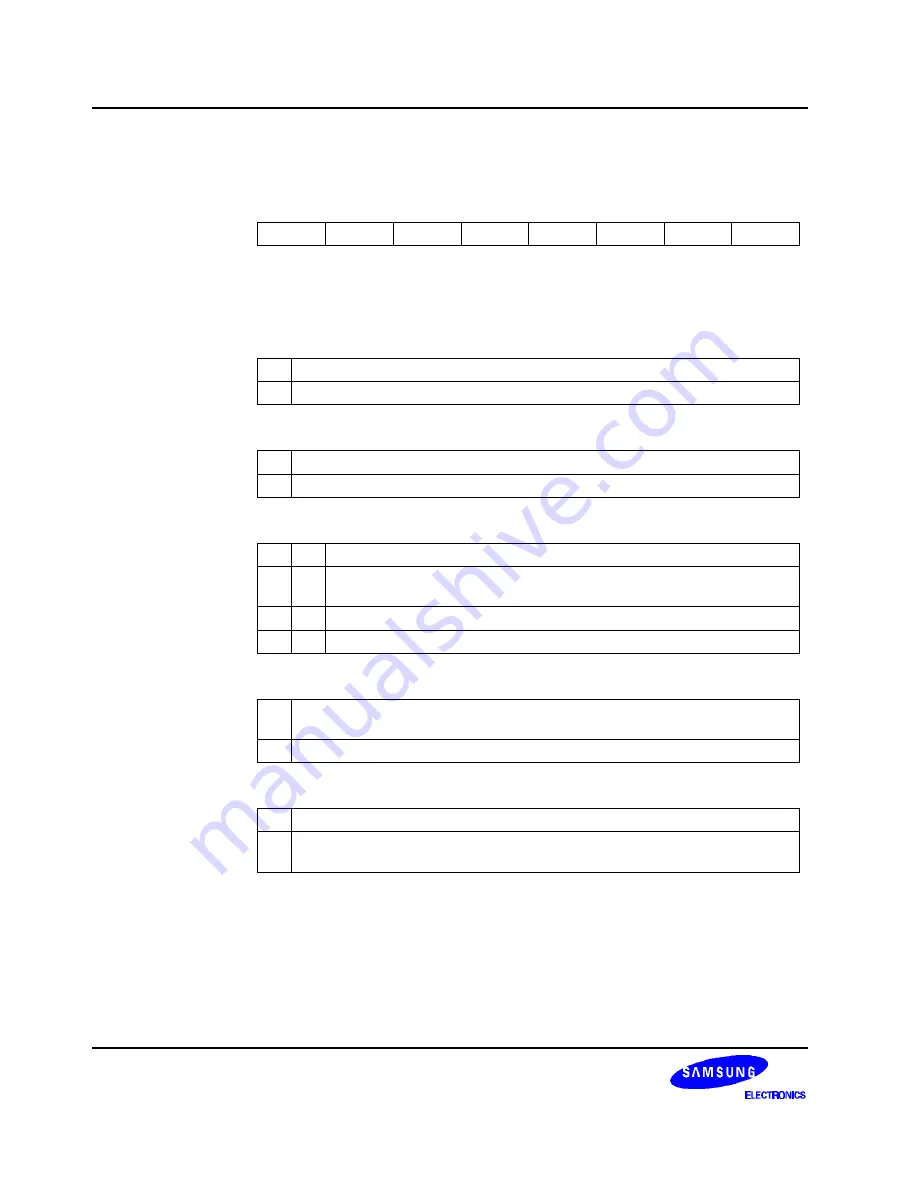

PSW

— Program Status Word

FB1H, FB0H

Bit

7

6

5

4

3

2

1

0

Identifier

C

SC2

SC1

SC0

IS1

IS0

EMB

ERB

RESET

Value

(1)

0

0

0

0

0

0

0

Read/Write

R/W

R

R

R

R/W

R/W

R/W

R/W

Bit Addressing

(2)

8

8

8

1/4/8

1/4/8

1/4/8

1/4/8

C

Carry Flag

0

No overflow or borrow condition exists

1

An overflow or borrow condition does exist

SC2–SC0

Skip Condition Flags

0

No skip condition exists; no direct manipulation of these bits is allowed

1

A skip condition exists; no direct manipulation of these bits is allowed

IS1, IS0

Interrupt Status Flags

0

0

Service all interrupt requests

0

1

Service only the high-priority interrupt(s) as determined in the interrupt

priority register (IPR)

1

0

Do not service any more interrupt requests

1

1

Undefined

EMB

Enable Data Memory Bank Flag

0

Restrict program access to data memory to bank 15 (F80H–FFFH) and to

the locations 000H–07FH in the bank 0 only

1

Enable full access to data memory banks 0, 1, 2, and 15

ERB

Enable Register Bank Flag

0

Select register bank 0 as working register area

1

Select register banks 0, 1, 2, or 3 as working register area in accordance with

the select register bank (SRB) instruction operand

NOTES

:

1.

The value of the carry flag after a RESET occurs during normal operation is undefined. If a RESET occurs during

power-down mode (IDLE or STOP), the current value of the carry flag is retained.

2.

The carry flag can only be addressed by a specific set of 1-bit manipulation instructions. See Section 2 for

detailed information.

Summary of Contents for C2316

Page 30: ...ADDRESS SPACES KS57C2308 P2308 C2316 P2316 2 22 NOTES ...

Page 168: ...SAM47 INSTRUCTION SET KS57C2308 P2308 C2316 P2316 5 94 NOTES ...

Page 170: ......

Page 206: ...POWER DOWN KS57C2308 P2308 C2316 P2316 8 8 NOTES ...

Page 210: ...RESET KS57C2308 P2308 C2316 P2316 9 4 NOTES ...

Page 222: ...I O PORTS KS57C2308 P2308 C2316 P2316 10 12 NOTES ...

Page 272: ...LCD CONTROLLER DRIVER KS57C2308 P2308 C2316 P2316 12 24 NOTES ...

Page 280: ...SERIAL I O INTERFACE KS57C2308 P2308 C2316 P2316 13 8 NOTES ...

Page 294: ...MECHANICAL DATA KS57C2308 P2308 C2316 P2316 15 2 NOTES ...

Page 310: ...KS57P2308 P2316 OTP KS57C2308 P2308 C2316 P2316 16 16 NOTES ...

Page 318: ......

Page 320: ......

Page 322: ......

Page 325: ......

Page 327: ......