70

CMX32M cpuModule

BDM-610000075

Rev B

Chx

: Writing a ‘1’ enabled generation of an interrupt when the same bit of the CH_IRQ_STAT register goes high.

PACER_DIVIDER

: A 32-bit divider for the pacer clock. Read-only during sampling. When the pacer clock rolls

over, the Channel Gain Table is scanned at a rate of 100kHz. This register should only be modified when sampling

is stopped. The time between scans is:

The maximum sample rate is 100kHz. The maximum scan rate is 100kHz divided by the number of channels

scanned. Any PACER_DIVIDER value that would yield a sample rate of greater than 100kHz has undefined

results, except a PACER_DIVIDER value of 0x00000000 will sample at the fastest rate possible.

CUR_BUFFER_OFFSET

: The offset into the current 4kB DMA buffer where data will be written next. This is the

same value for every channel, i.e. the channels are always synchronized.

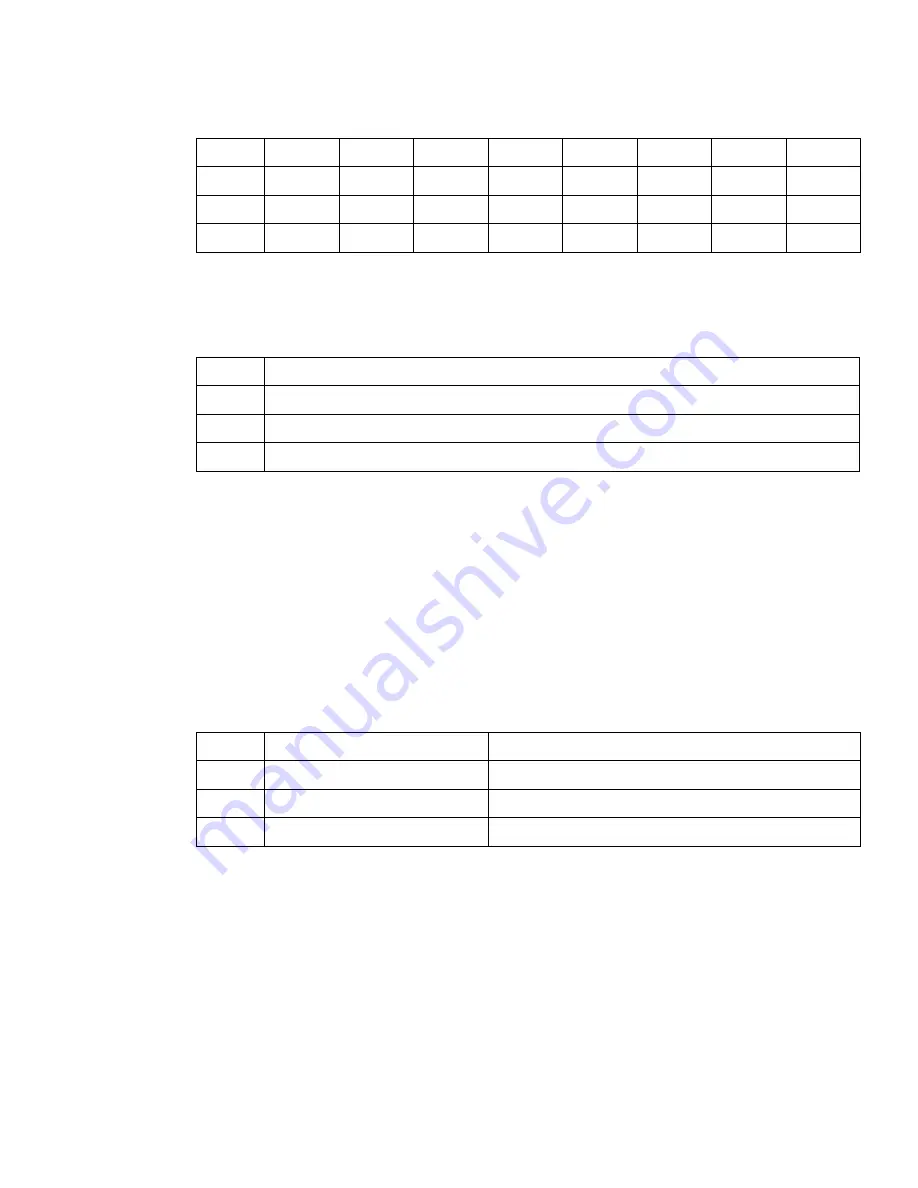

0x9E3:

CH_IRQ_ENA Register

Bit

7

6

5

4

3

2

1

0

Mode

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

Field

Ch8

Ch7

Ch6

Ch5

Ch4

Ch3

Ch2

Ch1

0x9E4:

PACER_DIVIDER Register

Bit

31

0

Mode

R/W

Default

0x00000000

Field

PACER_DIVIDER

ScanRate

40MHz

PACERDIVIDER

1

+

(

)

--------------------------------------------------------

=

0x9E8: CUR_BUFFER_OFFSET

Register

Bit

16

12

11

0

Mode

R

R

Default

0

0

Field

Reserved

CUR_BUFFER_OFFSET

Summary of Contents for BDM-610000075

Page 3: ... Accessing the Analog World www rtd com ISO9001 and AS9100 Certified CMX32M cpuModules ...

Page 4: ...iv CMX32M cpuModule BDM 610000075 Rev B ...

Page 30: ...22 CMX32M cpuModule BDM 610000075 Rev B ...

Page 60: ...52 CMX32M cpuModule BDM 610000075 Rev B ...

Page 102: ...94 CMX32M cpuModule BDM 610000075 Rev B ...

Page 116: ...108 CMX32M cpuModule BDM 610000075 Rev B ...