Renesas RA Family

RA2 Quick Design Guide

R01AN6060EU0100 Rev.1.00

Page 40 of 44

Sep.14.21

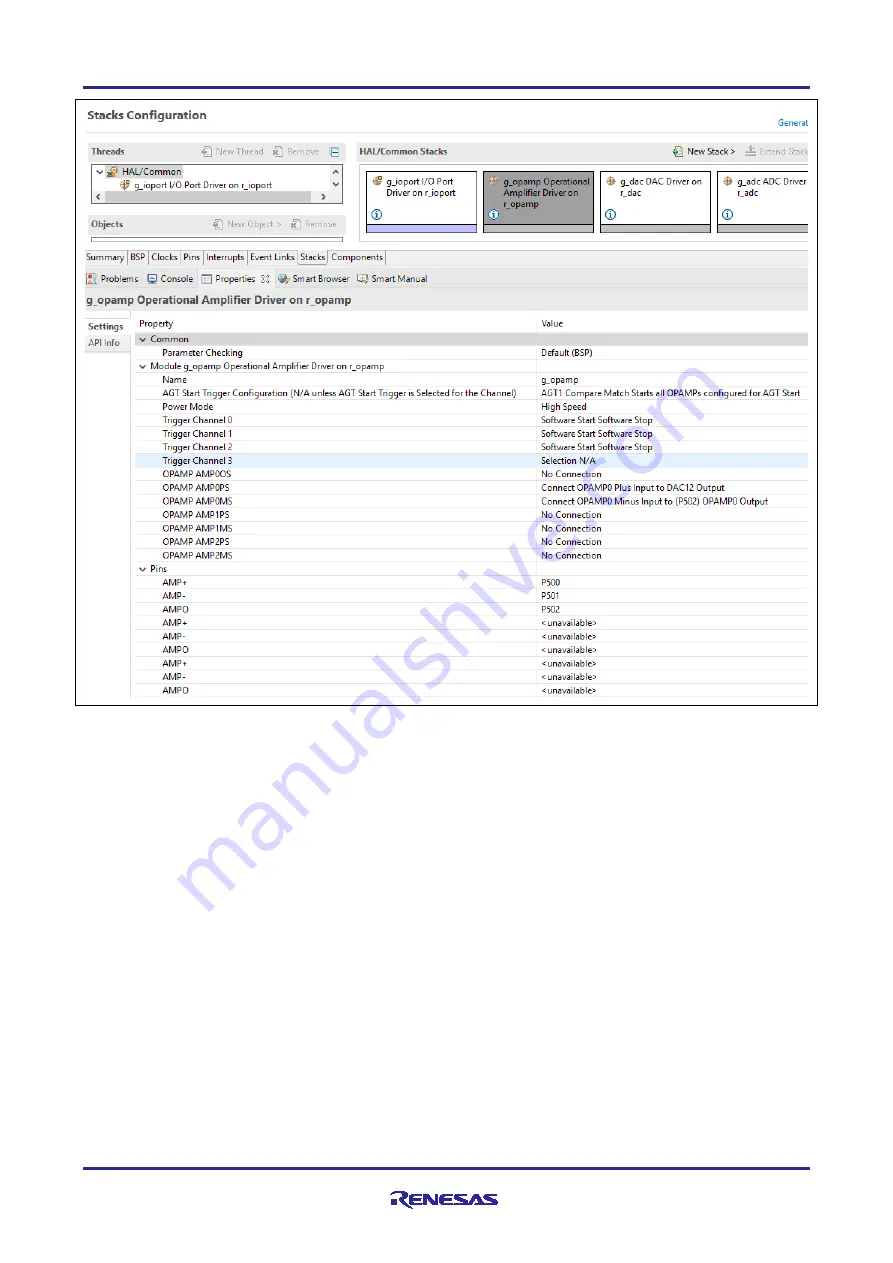

Figure 31. Example of Setting A RA2A1’s OPAMP Using FSP Configurator

After an OPAMP is set up by FSP Configurator, you can use OPAMP driver’s APIs such as

R_OPAMP_Open and R_OPAMP_Start to initialize and start OPAMP operation. Refer to the “Operational

Amplifier (OPAMP)” chapter in RA2A1 Hardware User’s Manual and FSP User’s Manual for more details.

16. General Layout Practices

16.1 Digital Domain vs. Analog Domain

Renesas RA2 Microcontroller devices have three primary types of pin functions: Power, Digital, and Analog.

Generally, power pins are dedicated for voltage and reference input and do not have multiple functions.

Power pins are typically dedicated to specific portions, or domains, within the MCU. For example, the main

supply voltage for the MCU will provide power to the digital core, many of the digital peripheral functions and

many of the digital I/O pins. The digital domain can be defined as the digital circuitry, digital I/O pins, and the

related power pins. Power pins which are designated for analog functions (such as AVCC0 and the

associated AVSS0) supply specific analog circuitry within the MCU, which is separate from the digital domain

circuitry. The analog domain can be defined as the analog circuitry, analog I/O pins, and the related power

pins.

Digital signals are typically repetitive, switched patterns that are associated with periodic clocks. The

transitions on digital signals tend to be relatively sharp edges, with stable levels of high or low between the

transitions. Each signal must be stable at an acceptable voltage level, referred to as a logic state, within a

specified timeframe. The state of the signal is typically sampled at predetermined clock intervals, using the

edge transition of a clock to evaluate the associated data signals. Small variations in the voltage level of

digital signals are typically acceptable, as long as the level remains within a specified range. However, large