198

Rabbit 3000 Microprocessor

When the spectrum spreader is engaged, the frequency is modulated, and individual clock

cycles may be shortened or lengthened by an amount that depends on whether the clock

doubler is engaged and whether the spectrum spreader is set to the normal or strong set-

ting. The frequency modulation amplitude and the change in clock cycle length is greater

at lower voltages or higher temperatures since it is sensitive to process parameters. The

spectrum spreader also introduces a time offset in the system clock edge and an equal off-

set in edges generated relative to the system clock. A feedback system limits the worst

case time error of any signal edge derived from the system clock to plus or minus 20 ns for

the normal setting and plus or minus 40 ns for the strong setting at 3.3 V. The maximum

time offset is inversely proportional to operating voltage. The time error will not usually

interfere with communications channels, except perhaps at the extreme upper data rates.

More details on dealing with the clock variation introduced are available elsewhere (see

Chapter 16, “AC Timing Specifications”).

If the input oscillator frequency is 4 MHz or less the spectrum spreader modulation of fre-

quency will enter the audio range of 20 kHz or less and may generate an audible whistle in

FM stations. For this reason it may be desirable to disable the spreader for low speed oscil-

lators (where it is probably unnecessary anyway). However, in practical cases the whistle

may not be audible due to the very low level of the interference from a system with low

oscillator frequency and the spectrum spreader engaged. Each halving of clock frequency

reduces the amplitude of the harmonics at a given frequency by 6 dB or more.

The effect of pure harmonic noise on an FM station is to either completely block out a sta-

tion near the harmonic frequency or to disturb reception of that station. If the spectrum

spreader is engaged then interference will be spread across the band but will generally be

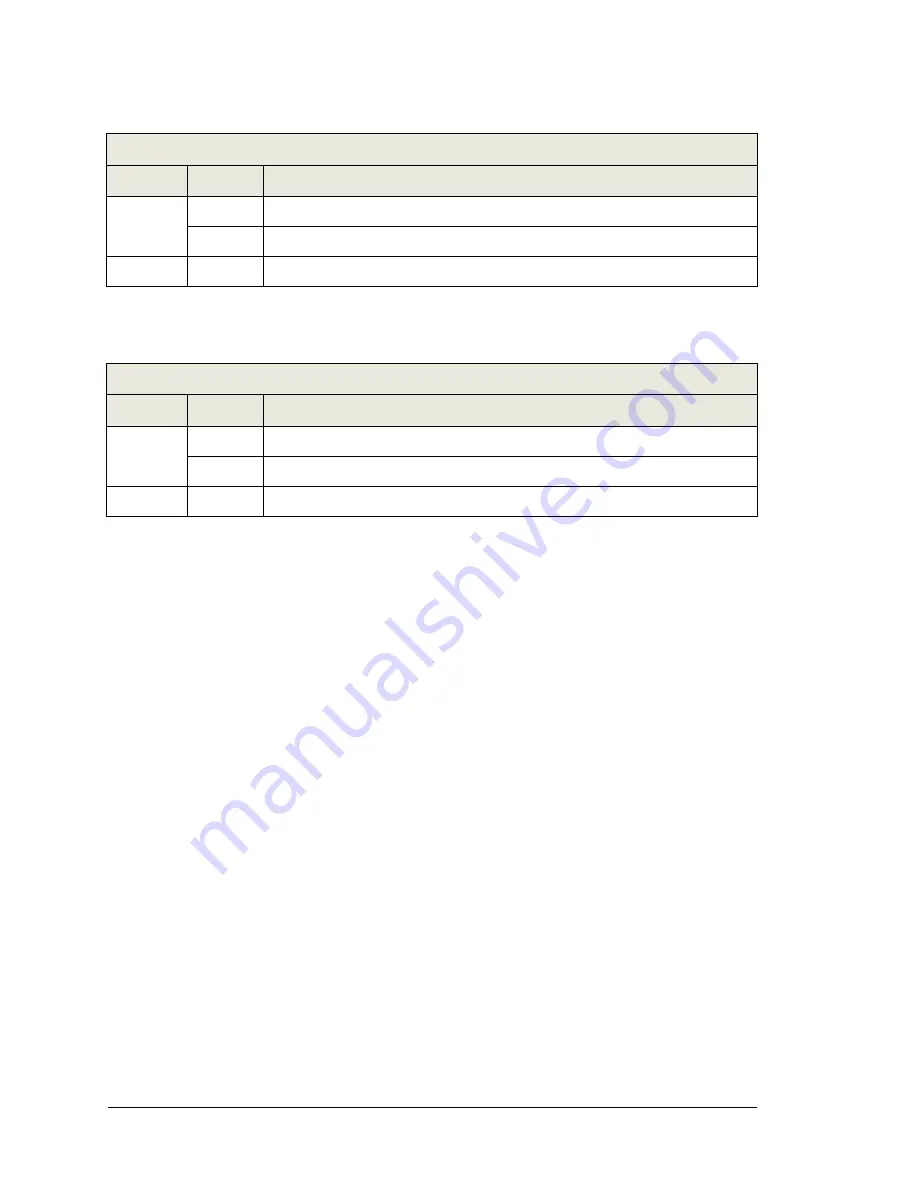

Table 15-1. Spread Spectrum Enable/Disable Register

Global Clock Modulator 0 Register

(GCM0R)

(Address = 0x0A)

Bit(s)

Value

Description

7

0

Enable normal spectrum spreading.

1

Enable strong spectrum spreading.

6:0

These bits are reserved.

Table 15-2. Spread Spectrum Mode Select

Global Clock Modulator 1 Register

(GCM1R)

(Address = 0x0B)

Bit(s)

Value

Description

7

0

Disable the spectrum spreader.

1

Enable the spectrum spreader.

6:0

These bits are reserved.

Summary of Contents for 3000

Page 1: ...Rabbit 3000 Microprocessor User s Manual 019 0108 020426 A...

Page 8: ...Rabbit 3000 Microprocessor...

Page 28: ...20 Rabbit 3000 Microprocessor...

Page 73: ...User s Manual 65 6 RABBIT INTERNAL I O REGISTERS...

Page 122: ...114 Rabbit 3000 Microprocessor...

Page 138: ...130 Rabbit 3000 Microprocessor...

Page 150: ...142 Rabbit 3000 Microprocessor...

Page 188: ...180 Rabbit 3000 Microprocessor...

Page 208: ...200 Rabbit 3000 Microprocessor...

Page 228: ...220 Rabbit 3000 Microprocessor...

Page 232: ...224 Rabbit 3000 Microprocessor...

Page 238: ...230 Rabbit 3000 Microprocessor...

Page 260: ...252 Rabbit 3000 Microprocessor...

Page 266: ......