Instruction Reference Manual

111

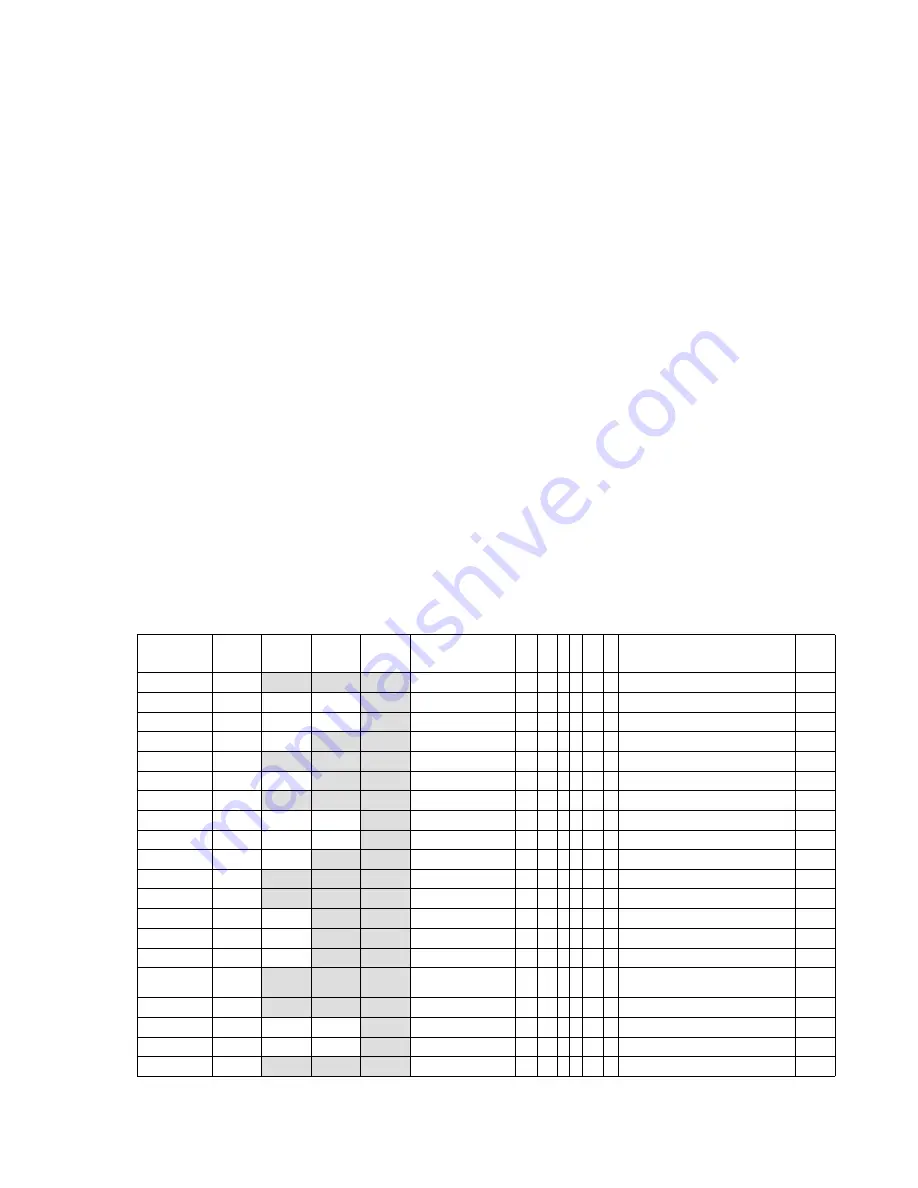

6. Quick Reference Table

Key

•

Instruction

: The mnemonic syntax of the instruction.

•

Opcode

: The binary bytes that represent the instruction.

•

Clock cycles

: The number of clock cycles that the instruction takes to complete. The numbers in

parenthesis are a breakdown of the total clocks. For more information, please see Table 1: "Clocks

Breakdown" on page 7.

•

A

: How the ALTD prefix affects the instruction. For more information, please see Table 2: "ALTD

(“A” Column) Symbol Key" on page 8.

•

I

: How the IOI or IOE prefixes affect the instruction. For more information, please see Table 3: "IOI

and IOE (“I” Column) Symbol Key" on page 8. A “b” in this column indicates that the prefix applies to

both source and destination.

•

S

;

Z

;

LV

;

C

: These columns denote how the instruction affects the flags. For more information, please

see Table 4: "Flag Register Key" on page 8.

•

Operation

: A symbolic representation of the operation performed.

•

N/M/P

: An “N” in this column indicates that the instruction has been added to the Z180 instruction

set by the Rabbit 2000/3000. An “M” indicates that this instruction is from the Z180, but has been

modified. A “P” indicates a privileged instruction.

Instruction

Opcode

byte 1

Opcode

byte 2

Opcode

byte 3

Opcode

byte 4

Clock cycles

A

I

S Z LV C

Operation

N/M/P

ADC A,(HL)

10001110

5 (2,1,2)

fr

s

*

*

V

*

A = A + (HL) + CF

ADC A,(IX+d)

11011101

10001110

----d---

9 (2,2,2,1,2)

fr

s

*

*

V

*

A = A + (IX+d) + CF

ADC A,(IY+d)

11111101

10001110

----d---

9 (2,2,2,1,2)

fr

s

*

*

V

*

A = A + (IY+d) + CF

ADC A,n

11001110

----n---

4 (2,2)

fr

*

*

V

*

A = A + n + CF

ADC A,r

10001-r-

2

fr

*

*

V

*

A = A + r + CF

ADC HL,ss

11101101

01ss1010

4 (2,2)

fr

*

*

V

*

HL = HL + ss + CF

ADD A,(HL)

10000110

5 (2,1,2)

fr

s

*

*

V

*

A = A + (HL)

ADD A,(IX+d)

11011101

10000110

----d---

9 (2,2,2,1,2)

fr

s

*

*

V

*

A = A + (IX+d)

ADD A,(IY+d)

11111101

10000110

----d---

9 (2,2,2,1,2)

fr

s

*

*

V

*

A = A + (IY+d)

ADD A,n

11000110

----n---

4 (2,2)

fr

*

*

V

*

A = A + n

ADD A,r

10000-r-

2

fr

*

*

V

*

A = A + r

ADD HL,ss

00ss1001

2

fr

-

-

-

*

HL = HL + ss

ADD IX,xx

11011101

00xx1001

4 (2,2)

f

-

-

-

*

IX = IX + xx

ADD IY,yy

11111101

00yy1001

4 (2,2)

f

-

-

-

*

IY = IY + yy

ADD SP,d

00100111

----d---

4 (2,2)

f

-

-

-

*

SP = SP + d

N

01110110

2

-

-

-

-

alternate register destination

for next instruction

N

AND (HL)

10100110

5 (2,1,2)

fr

s

*

*

L

0

A = A & (HL)

AND (IX+d)

11011101

10100110

----d---

9 (2,2,2,1,2)

fr

s

*

*

L

0

A = A & (IX+d)

AND (IY+d)

11111101

10100110

----d---

9 (2,2,2,1,2)

fr

s

*

*

L

0

A = A & (IY+d)

AND HL,DE

11011100

2

fr

*

*

L

0

HL = HL & DE

N

Summary of Contents for 2000

Page 2: ...ii Rabbit 2000 3000 Microprocessor...

Page 4: ...iv Rabbit 2000 Microprocessor...

Page 16: ...12 Rabbit 2000 3000 Microprocessor...

Page 112: ...108 Rabbit 2000 3000 Microprocessor...

Page 120: ...ii Rabbit 2000 3000 Microprocessor...