5G Module Series

RM505Q-AE Hardware Design

RM505Q-AE_Hardware_Design 36 / 79

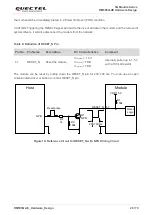

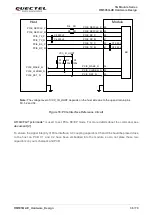

Host

Module

PCIE_REFCLK_P

PCIE_REFCLK_M

PCIE_RX_P

PCIE_RX_M

PCIE_TX_P

PCIE_TX_M

BB

PCIE_REFCLK_P

PCIE_REFCLK_M

PCIE_RX_P

PCIE_RX_M

PCIE_TX_P

PCIE_TX_M

55

53

49

47

43

41

PCIE_CLKREQ_N

PCIE_RST_N

PCIE_WAKE_N

PCIE_CLKREQ_N

PCIE_RST_N

PCIE_WAKE_N

54

52

50

Note:

The voltage level of VCC_IO_HOST depends on the host side due to the open drain in pins

50, 52 and 54.

C6 220 nF

C5 220 nF

C2 220 nF

C1 220 nF

R1

100k

R2

100k

R3

100k

VCC_IO_HOST

R5 0R

R4 0R

Figure 18: PCIe Interface Reference Circuit

AT+QCFG="pcie/mode"

is used to set PCIe RC/EP mode. For more details about the command, see

document [2]

.

To ensure the signal integrity of PCIe interface, AC coupling capacitors C5 and C6 should be placed close

to the host on PCB. C1 and C2 have been embedded into the module, so do not place these two

capacitors on your schematic and PCB.