79

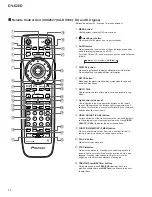

DV-626D

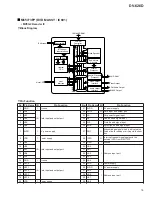

YSS912C (JCKB ASSY : IC501)

• DTS Decoder

•

Block Diagram

Microcomputer

Interface

Control

Signal

Control

Signal

Control Register

SDIA

Interface

Input

Buffer

SDOA

Interface

SDIB

Interface

SDOB

Interface

Data

RAM

Outernal RAM

Interface

ERA MUSE

SDIB

SEL

SDOA CKSEL

CRC

SDIA

SEL

IPORT0 - 7

/SDBCK0

/CS

SO

SI

SCK

OPORT0 - 7

66

57

SDBCK0

83

68

67

69

/CSB

65

24*24

Main DSP

AC-3 Pro Logic/DTS

Decoder

RAM for Delay

PLL

Calculation

Clock

(30MHz)

STREAM0 - 7

L,R

24*16

Sub DSP

Coefficient

•

Program

RAM

SDIB CKSEL

SDOB CKSEL

SI

SCK

32 - 39

72 - 79

99 - 92

SDWCK0

82

SDIA0

84

SDIA1

85

SURENC

56

8

9

19

KARAOKE

55

MUTE

54

CRC

53

AC3DATA

XI

XO

CPO

24

SDOA0

23

SDOA1

22

SDOA2

5

SDIB0

6

SDIB1

7

SDIB2

12

SDIB3

2

RAMCEN

88

RAMWEN

89

RAMOEN

15

OVFB

18

SDOB3

45

SDOB2

46

SDOB1

47

SDOB0

49

SDWCK1

48

SDBCK1

SDIB3

RAMA0 - 16

17

DTSDATA

16

NONPCM

52

LS,RS

C,LFE

3,4,25-29,

42-44,58-59

,61,64,70,

86,87