Jumpers

©

PHYTEC Messtechnik GmbH 2006 L-658e_5

19

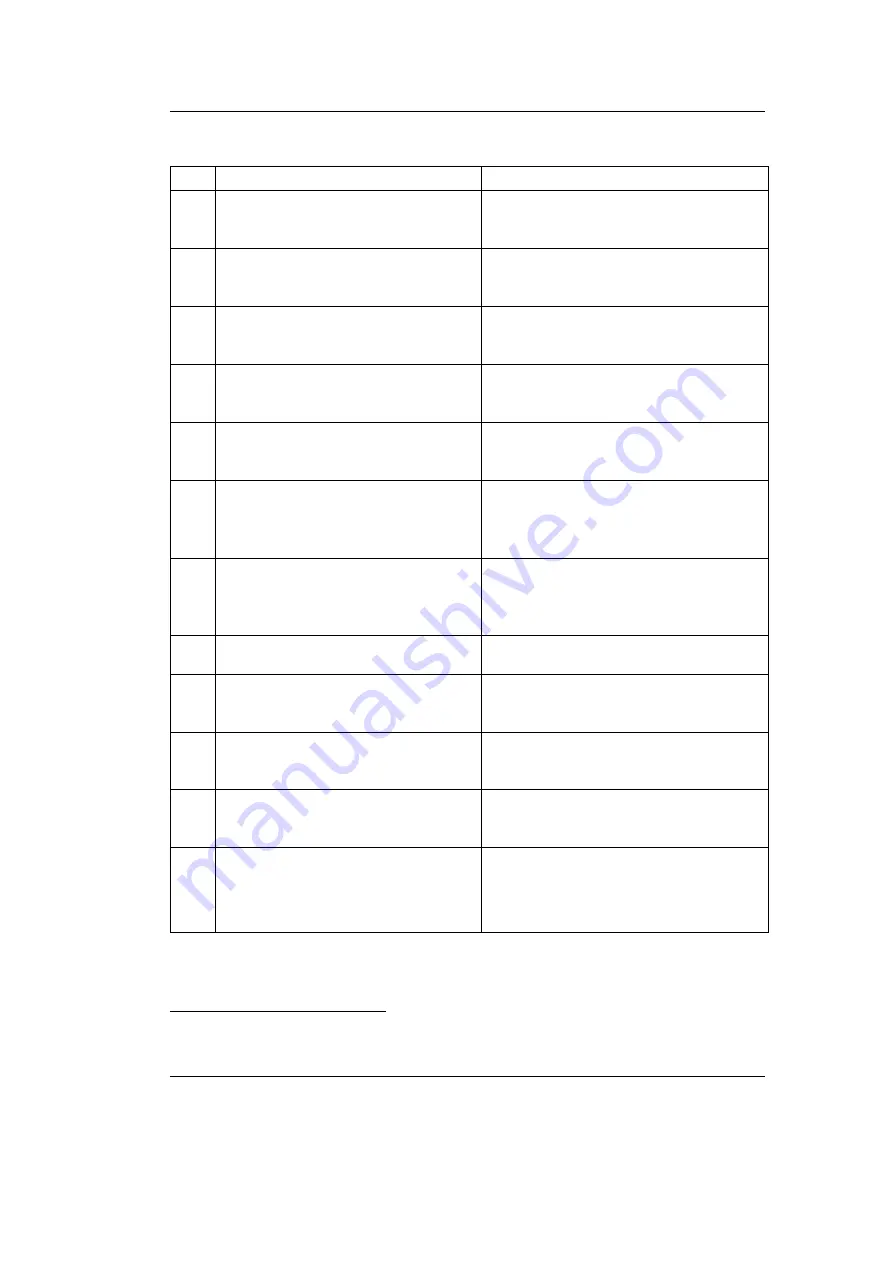

The jumpers (J = solder jumper) have the following functions:

Default Setting

Alternative Setting

J200

1 + 2

P08 as TxD1 with RS-232

level available at X700C23

2 + 3

P08 of the µC available as

standard I/O or TxD1 with TTL

level at pin X700C23

J201

1 + 2

P00 as TxD0 with RS-232

level available at X700D23

2 + 3

P00 of the µC available as

standard I/O or TxD0 with TTL

level at pin X700D23

J202

1 + 2

P09 as RxD1 with RS-232

level available at X700C21

2 + 3

P09 of the µC available as

standard I/O or RxD1 with TTL

level at pin X700C21

J203

1 + 2

P01 as RxD0 with RS-232

level available at X700D22

2 + 3

P01 of the µC available as

standard I/O or RxD0 with TTL

level at pin X700D22

J204

1 + 2

VDD_V3V3 as reference

voltage for CPU internal

A/D converter

2 + 3

Reference voltage for internal

A/D converter can be supplied

via pin X700D50

J205

closed

/CS0 connected with /CSF0

(only if CPLD U202 is not

populated)

open

/CS0 of the controller

connected with CPLD U202,

CPLD generates /CSF0 - /CSF1

signals

J206

closed

/CS1 connected with /CSR0

(only if CPLD U202 is not

populated)

open

2

/CS1 of the controller

connected with CPLD U202,

CPLD generates /CSR0 -

/CSR1 signals

J207

open

MCKO signal not routed to

Molex connector pin

closed

MCKO signals routed to Molex

pin X700B1

J208

open

Flash configuration input 1

of CPLD U202 connected to

VCC via 10k pull-up

closed

Flash configuration input 1 of

the CPLD connected to GND

J209

open

Flash configuration input 2

of CPLD U202 connected to

VCC via 10k pull-up

closed

Flash configuration input 2 of

the CPLD connected to GND

J210

open

RAM configuration input 1

of CPLD U202 connected to

VCC via 10k pull-up

closed

RAM configuration input 1 of

the CPLD connected to GND

J211

open

RAM configuration input

2 of CPLD U202

connected to VCC via

10k pull-up

closed RAM configuration input 2

of the CPLD connected to

GND

1

:

Applies to standard modules without optional features, minimal memory configuration.

2

:

Default on all other configuration options of the phyCORE-LPC2292/94.

Summary of Contents for phyCORE-LPC2292/94

Page 12: ...phyCORE LPC2292 94 PHYTEC Messtechnik GmbH 2006 L 658e_5...

Page 76: ...phyCORE LPC2292 94 64 PHYTEC Messtechnik GmbH 2006 L 658e_5...

Page 80: ...phyCORE LPC2292 94 68 PHYTEC Messtechnik GmbH 2006 L 658e_5...

Page 88: ...phyCORE LPC2292 94 76 PHYTEC Me technik GmbH 2006 L 658e_5...

Page 132: ...phyCORE LPC2292 94 120 PHYTEC Me technik GmbH 2006 L 658e_5...

Page 136: ...phyCORE LPC2292 94 124 PHYTEC Me technik GmbH 2006 L 658e_5...

Page 142: ...phyCORE LPC2292 94 130 PHYTEC Me technik GmbH 2006 L 658e_5...

Page 144: ...Published by PHYTEC Me technik GmbH 2006 Ordering No L 658e_5 Printed in Germany...