11 - 4

11 - 4

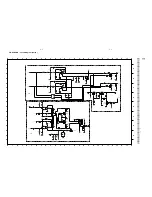

CIRCUIT DIAGRAM - Part 3

NC

NC

TD-

CTD

TX+

CTX

TX-

TD+

XTAL

FIFOSEL

SA

PSEN

TEST

TPI

EE

TPO

ACT

COL

SD

3A3

3R3

18A

VCC

VCC3IO

VCCK

3A3

TCLK

TCLK_EN

+

-

CK

CS

DIO

IOIS16

RSET_BG

GND

GND

3R3

18A

PME

ISPEED

IRQ

IFULL

I_LK

-

+

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

V18F

IN

OUT

0

1

2

3

4

5

CS

RST

WR

RD

AEN

1

2

RX+

CRX

RX-

RD+

CRD

RD-

3

2324 F5

2326 H5

2327 G3

2328 A9

2329 A9

2330 A9

2331 A9

2332 B8

2333 B9

OPTION

12

13

A

B

C

D

E

OPTION

DEBUG

F

H

OPTION

OPTION

F

G

H

A

B

C

D

E

1302 G2

2317 C5

2318 F6

2319 F7

2320 G5

2321 B11

2322 B12

2323 F5

3310-2 C8

1

3310-4 C8

3314-1 D8

3314-2 D8

3314-3 D8

3314-4 D8

3315-1 D8

3315-2 D8

2

4

5

6

7

8

9

10

11

OPTION

13

10

2

3

4

5

6

7

8

9

11

3315-3 D8

3315-4 D8

3319-1 D8

3319-2 D8

3319-3 D8

3319-4 D8

3323 C8

LAN INTERFACE

3329 E5

OPTION

3331 F5

2334 A9

2335 B9

2336 B9

2337 H5

2338 C11

2339 C8

2340 C8

2341 F5

G

3300-1 B11

1300 B11

3300-3 C11

3300-4 C11

3301-1 C11

3301-2 C11

3301-3 B11

3301-4 B11

3306 C11

3310-1 C8

3310-3 C8

OPTION

12

1

3359 B8

5305 F7

5311-1 G4

5311-2 F4

5311-3 F4

5312 A7

5315 A7

5316 A7

5317 C7

5318 A7

3330 F5

5321 G5

3333 F6

3334 F7

3336 F5

3338 B11

3339 F6

3340 F7

3341 F8

3342 F8

3011 C11

3344 F8

3300-2 C11

3349 G3

3350 A11

3351 C11

3352 C11

3353 D11

3354 D11

3355 E11

3357 D11

3358 E11

5304 C5

5319 A7

5322 B5

6300 F7

6301 F7

6302 F7

7301 B9

F301 C5

F302 G2

F303 G2

3343 B11

F305 G2

3346 G3

F307 G2

F308 A11

F304 G2

F306 G2

3301-1

1

8

6.3V

22R

2317

47u

22R

3300-4

4

5

1

2

3

16

15

14

TLA-6T118LF

5311-1

8

2332

220n

1

RX+

RX- 2

GND_RJ45 3

TX- 4

TX+ 5

GND_RJ45 6

7

S6B-PH-SM4-TB(LF)

1302

3349

75R

2M2

3338

2u2

2337

22R

4

5

1

8

3315-4

22R

3310-1

3306

22R

1n0

2338

6300

TLMY3100

TLMG3100

6301

6302

1u5

5304

TLMH3100

1%

3351

4K7

3333

100R

TLA-6T118LF

5311-3

220R

3341

F301

1

8 22R

3315-1

7

100n

2333

3300-2

22R

2

3

6 22R

3314-3

100n

2335

1u5

5322

3314-4

22R

4

5

220R

3344

5318

600R

75R

3346

F305

100n

2339

3310-2

22R

3319-2

22R

2

7

3

6

2

7

22R

3315-3

3314-2

22R

3300-1

22R

1

8

220n

2334

4K7

3359

3315-2

22R

2

7

3300-3

22R

3

6

5321

600R

600R

5305

100n

2326

22R

3301-3

3

6

2327

100n

3011

10K

1%

100R

3339

10K

3353

1%

12K1

3355

22R

3314-1

2336

100n

10p

2320

1%

100R

3330

F303

5312

600R

10p

2321

F302

4

5

2n2

2318

3301-4

22R

3342

220R

3340

100R

1%

25

44

10

24

43

59

60

54

62

61

56

57

13

12

3

4

6

7

9

5

1

28

27

40

39

38

37

36

35

34

33

48

47

46

45

42

41

32

31

30

29

55

23

15

14

22

53

64

17

50

49

21

19

18

8

26

58

2

11

63

16

7301

AX88796BLF

51

52

20

3352

22R

Φ

22R

3310-4

X5R

10u

2340

3329

100R

1%

3323

22R

1

8

2330

100n

22R

3319-1

3357

100K

100n

2331

22R

3310-3

1%

100R

3331

1

2

F306

1300

DSX530GA

25M

F308

F304

3319-4

22R

4

5

600R

5315

2n2

2323

100K

2341

100n

2

7

3358

3301-2

22R

F307

600R

5319

2K2

3343

5317

600R

TLA-6T118LF

5311-2

6

7

8

11

10

9

1%

100R

3334

6

3336

100R

1%

22R

3319-3

3

2328

100n

100n

2329

2324

2322

10p

100n

600R

5316

100n

2319

3350

+3V3_ETH

10K

10R

S_MPMC_A(7)

+1V8_ETH

S_MPMC_A(0:20)

+1V8_ETH

+3V3_ETH

S_ETHERNET_IRQ

3354

S_MPMC_D(3)

S_MPMC_D(4)

S_MPMC_D(5)

S_MPMC_D(6)

S_MPMC_D(7)

S_MPMC_D(8)

S_MPMC_D(9)

S_MPMC_D(10)

S_MPMC_D(11)

S_MPMC_D(12)

S_MPMC_D(13)

S_MPMC_D(14)

S_MPMC_D(15)

S_MPMC_D(0:15)

S_MPMC_STCS1_N

S_MPMC_WE_N

S_MPMC_OE_N

+3V3_ETH

S_ETHERNET_RESET

+3V3_ETH

+3V3_ETH

+3V3

+3V3_ETH

+3V3_ETH

S_MPMC_A(6)

S_MPMC_A(8)

S_MPMC_A(9)

S_MPMC_A(10)

S_MPMC_D(0)

S_MPMC_D(1)

S_MPMC_D(2)

( ETHERNET )