IC Data Sheets

8

.

8

.9

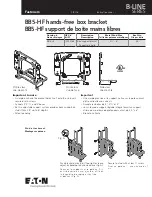

Diagram

, NJW1141M (IC U24)

Figure

8

-9 Internal block diagram and pin configuration

Block Dia

g

ram

Pin Confi

g

uration

1

8

4

3

0_

3

07_090204.ep

s

090204

Bia

s

AGC

CVA

CVB

CTH

CTL

GND

Vcc

Vref

TONE

-Ha

TONE

-Hb

TONE

-La

TONE

-Lb

OUTb

S

DA

S

CL

S

EL

S

EL

TONE

VOL2

AGC

TONE

VOL2

VOL1

VOL1

IN1a

IN2a

IN

3

a

IN4a

IN1b

IN2b

IN

3

b

IN4b

-2

d

B

-2

d

B

+4

.5

d

B

+4

.5

d

B

MONa

MONb

OUTa

I

2

C BU

S

Interface

11

CVB

DAC Output for Bch Volume & Balance

12

CVA

DAC Output for Ach Volume & Balance

l

a

n

i

m

r

e

T

y

l

p

p

u

S

r

e

w

o

P

+

V

6

1

17

Vref

Reference Volta

g

e

18

CTL

Pop Noi

s

e reduction for Ba

ss

Control

19

CTH

Pop Noi

s

e reduction for Treble Control

r

e

t

l

i

F

C

G

A

C

G

A

0

2

t

u

p

t

u

O

h

c

B

b

T

U

O

1

2

)

B

d

5

.

4

+

(

t

u

p

t

u

O

E

N

I

L

h

c

B

b

E

N

I

L

2

2

r

e

t

l

i

F

s

s

a

B

h

c

B

b

L

-

E

N

O

T

3

2

r

e

t

l

i

F

e

l

b

e

r

T

h

c

B

b

H

-

E

N

O

T

4

2

t

c

e

n

n

o

C

o

N

C

N

5

2

Bch Monitor Output

MONb

6

2

Bch Input4

IN4b

7

2

b

3

N

I

8

2

Bch Input

3

b

2

N

I

9

2

Bch Input2

b

1

N

I

0

3

Bch Input1

n

o

i

t

c

n

u

F

l

o

b

m

y

S

.

o

N

1

t

u

p

n

I

h

c

A

a

1

N

I

1

2 IN2a

Ach

Input2

3

IN

3

a

Ach Input

3

4 IN4a

Ach

Input4

t

u

p

t

u

O

r

o

t

i

n

o

M

h

c

A

a

N

O

M

5

t

c

e

n

n

o

C

o

N

C

N

6

r

e

t

l

i

F

e

l

b

e

r

T

h

c

A

a

H

-

E

N

O

T

7

r

e

t

l

i

F

s

s

a

B

h

c

A

a

L

-

E

N

O

T

8

)

B

d

5

.

4

+

(

t

u

p

t

u

O

E

N

I

L

h

c

A

a

E

N

I

L

9

t

u

p

t

u

O

h

c

A

a

T

U

O

0

1

1

3

S

DA

S

DA Data Input (I

2

)

S

U

B

C

14

S

CL

S

CL Clock Input (I

2

)

S

U

B

C

l

a

n

i

m

r

e

T

D

N

G

D

N

G

5

1

16

3

0

29

28

27

26

25

24

2

3

22

21

18

19

20

17

1

2

3

4

5

6

7

8

9

10

11

12

1

3

14

15

IN1a

IN2a

IN

3

a

IN4a

IN1b

IN2b

IN

3

b

IN4b

MONa

MONb

TONE-Ha

TONE-Hb

TONE-La

LINEa

TONE-Lb

LINEb

OUTa

OUTb

CVb

CTH

CTL

S

DA

S

CL

GND

Vref

V+

AGC

CVa

NC

NC

16