Interconnectivity

Page 21 of 22

Firmware Programming Guide for PDIUSBD12

Philips Semiconductors - Asia Product Innovation Centre

Visit

http://www.flexiusb.com

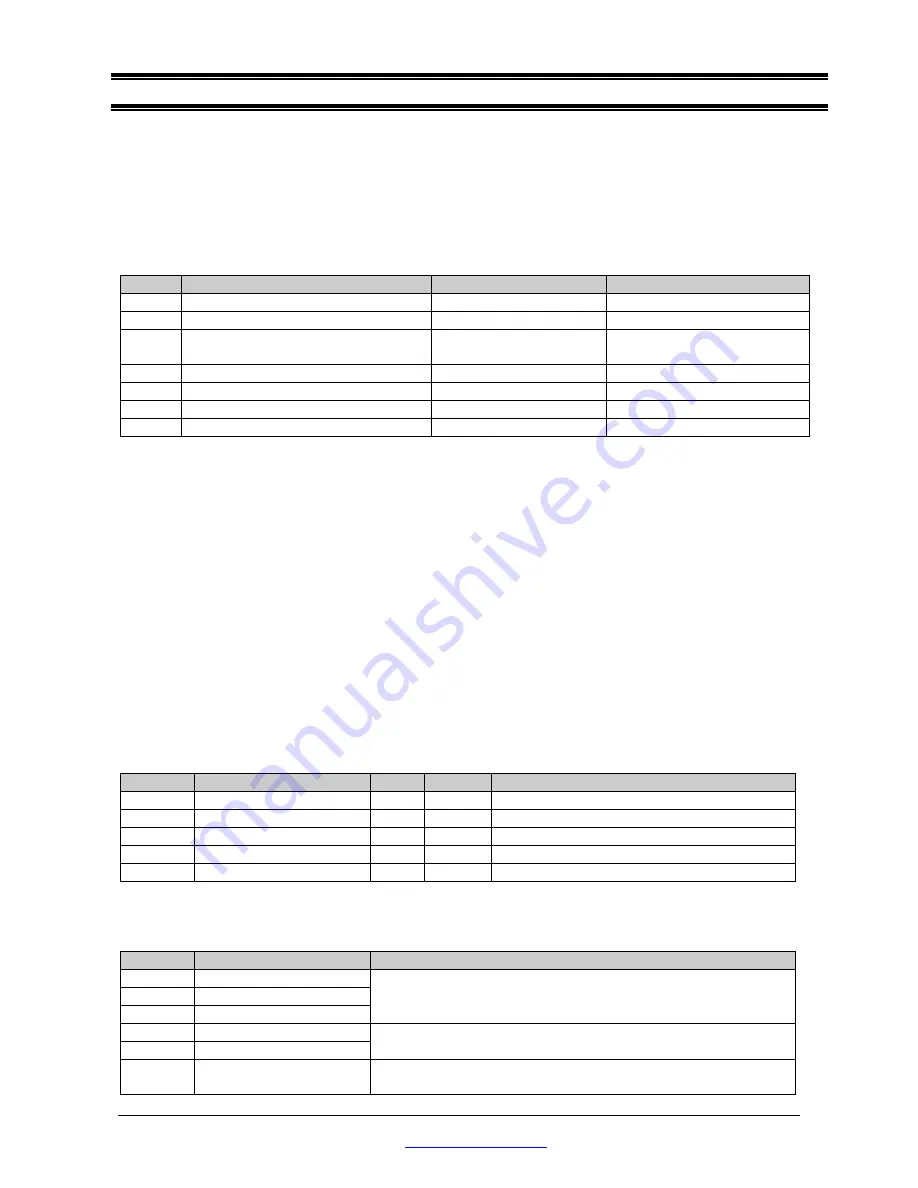

8.3 DMA Configuration Register

The D12's DMA operation is controlled by its DMA Configuration Register, which is set by the command Set

DMA. Not all the bits inside the register are related to the DMA operation. Bit 4 (Interrupt Pin Mode) together

with Bit 7 of Clock Division Factor (SOF-ONLY) controls D12 sources of interrupt.

The table below is a summary of the recommended register programming:

Bit

Name

DMA Mode

Non-DMA Mode

0 & 1

DMA Burst

‘1’ & ‘1’

Don’t care

2

DMA Enable

‘1’

‘0’

3

DMA Direction

‘1’ for IN token;

‘0’ for OUT token

Don’t care

4

Auto Reload

‘0’

Don’t care

5

Interrupt Pin Mode

‘0’

‘0’

6

Endpoint 4 Interrupt Enable

‘0’

‘1’

7

Endpoint 5 Interrupt Enable

‘0’

‘1’

By default, both D12 and DMAC are not in auto-reload mode. We do not want the device's DMA "auto-restart"

because this is a protocol-based operation, that is, under host's control. At EOT, both of D12 and DMA

controller's DMA will be disabled. The firmware needs to re-enable them to restart DMA transfer upon

receiving Setup DMA Request from the host.

Please also note that the interrupt from endpoints 4 and 5 are disabled in DMA mode. Servicing interrupt on

these endpoints is unnecessary and has a potential flaw during the DMA transfer. DMA can be treated as the

highest "interrupt" that happens between any CPU instructions, even inside ISR. Any routines that may want to

be used to check DMA status are not reliable because the DMA status during the transfer may change at any

time.

8.4 Setup DMA Request

Setup DMA request is a vendor request that is sent through control pipe. In PDIUSBD12 sample firmware and

Applet, this is done by IOCTL_WRITE_REGISTER, which is defined by Microsoft Still Image USB Interface

in Windows 98 DDK. The device's request is described below.

Offset

Field

Size

Value

Comments

0

BmRequestType

1

0x40

Vendor request, device to host

1

Brequest

1

0x0C

Fixed value for IOCTL_WRITE_REGISTER

2

Wvalue

2

0

Offset, set to zero

4

Windex

2

0x0471

Fixed value of Setup DMA Request

6

Wlength

2

6

Data length of Setup DMA Request

The details requested by the DMA operation are sent in the data phase after the device's request. The sample

firmware and Applet use a proprietary definition, which is shown below:

Offset

Field

Comments

0

Address [7:0]

The start address of requested DMA transfer.

1

Address [15:8]

2

Address [23:16]

3

Size [7:0]

The size of transfer.

4

Size [15:8]

5

Command

Bit 7: ‘1’ start DMA transfer

Bit 0: ‘1’ IN token; ‘0’ OUT token