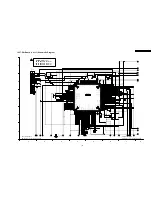

13.49. D-Board Block Diagram (50inch)

CLKD0

CLKD1

TXD_PC

RXD_PC

SDA2

SCL2

SDA1

IIC_CONT

SCL1

LED_G

LED_R

REMOCON

LED_G

LED_R

REM

SOS7

PANEL_MAIN_ON

PS_SOS

PS_SOS

PANEL_MAIN_ON

ALARM

READY

READY

ALARM

FAN_CONT

FAN_SOS

ECO_ON

F_STBY_ON

FAN_CONT

FAN_SOS

ECO_ON

F_STBY_ON

CLKM_IN

FREE_RUN

IIC_INT

DRVMUTE

NCE

DCLK

NCS

DATA0

CONF_DONE

DCLK

NCE

ASDI0

NCONFIG

CONF_DONE

NCONFIG

DATA0

NCS

ASDI0

TXD_PC

RXD_PC

IIC_CONT

IIC_INT

SDA2

SCL2

SDA1

SCL1

SOS2

SOS9

SOS2

SOS9

CLKU0

CLKU2

CLKU3

CLKD3

CLKD2

CLKU1

X9200

R9028

R 10bit

Scan Control DATA 13bit

IIC/INT

G 10bit

B 10bit

IIC_CONT

SCL2

B 10bit

SDA1

R 10bit

SDA2

SCL1

Sustain Control DATA 6bit

G 10bit

46

IC9502

8

27

PROCESSOR

DATA

DRIVER

7

TO C54

TO C55

11

6

85

12

84

D4

67

10

TXD1

66

RXD1

IIC_CONT

30

IIC_INT

LVDS

DISCHARGE

CONTROL

STB_SDA1

21

LEVEL CONVERTER

STB_SCL2

22

28

65

Voltage

26

STB_SDA2

78

49

IC9500

50

FPGA/SYNC/OSD/DISCHARGE CONTROL

5

55

NRST

XRST

NEW PLASMA AI

SUB-FIELD

PLASMA AI/SUB FIELD PROCESSOR

IC9003

IC9303

MICOM

XIN

XOUT

X9000

53

9.216MHz

IC9005,06

52

RESET

IC9004

RESET

28

RESET

STB3.3V

29

5

STB_SCL1

Video DATA

66bit(UA,UB,UCO-15)

3.3V

5V

Low

3.3V

5V

Video DATA

66bit(DA,DB,DC0-15)

D33

D34

10

DATA R

L-DOWN

DATA L

R-DOWN

DATA R TIMING

DATA L TIMING

5V_DET

56

57

TO DG3

D3

DRV_SOS2

DRV_SOS9

99

97

92

DRV_SOS7

72

READY

ALARM

71

1

AVR

AVR STB3.3V

2

DRVMUTE

STB5V_M

STB3.3V

4

IC9008

IIC_DATA1

IIC_CLK1 19

TUNER_SUB_ON

6

ALARM

FAN_SOS

8

FAN_CONT(FAN_MAX)

7

3

DISPEN

4

READY

PANEL_STB_ON

1

14

11

20

ECO_ON

4

2

RXD

TXD

6

D5

0+LVDSCLK

E+LVDSCLK

E-LVDS2

14

TO DG5

18

E-LVDS3

E+LVDS0

16

7

15

11

12

E-LVDS1

10

4

E-LVDS4

1

0-LVDSCLK

9

E-LVDS0

2

E-LVDSCLK

E+LVDS2

E+LVDS1

17

E+LVDS4

5

E+LVDS3

LVDS_DET

STBY5V

+5V

D25

PS_SOS

9

PANEL_MAIN_ON

ECO_ON

1

+5V

7

FAN_SOS

2

13

+12V

15

+12V

FAN_CONT

14

17

16

3

10

TO P25

F_STBY_ON

nCS

15

17

8

nCE

6

DATA0

7

CONF_DONE

PDB0

1

nCONFIG

PSTB

5

ASDIO

3

11

PSLCT

PBUSY

9

D6

DCLK

13

19

XRST

PDB1

18

16

DCDC_ON

st-r

IC9300

CONVERTER

XRST

CTI/TINT

WB-ADJ

I/P

COLOR

FORMAT CONVERTER/RGB PROCESSOR

CONVERTER

CONTRAST

FORMAT

Differential

Signaling

RECEIVER

FPGA CONTROL

OSD

R,G,B,HD,VD,CK

14

19

PS_SOS

98

PANEL_MAIN_ON

48

P_ON/OFF

41

Q9003

Q9012

Q9013

Q9008

Q9009

P3V_SCL2

P3V_SDA2

69

LED_R

REM_IN

70

10

LED_G

TO SC20

D20

2

9

13

20

SCAN

DATA

11

1

DRV_SOS7

P5V

3

6

D8

2

LED_R

REMOCON

LED_G

Q9010

35

55

34

31

DATA DRIVE

5V_DET

65

68

58

64

POWER

FEED BACK

DATA

56

DRVRST

57

DRVRST_DATA

SUSTAIN

DATA

57

64

1

4

DRV_SOS9

DRV_SOS2

Q9011

R0

B0

VD

HD DCK

G9

R9

B9

PICTURE OUTPUT

DCK

G0

P3V_SCL1

P3V_SDA1

P3V_SDA2

P3V_SCL2

Q9000

P12V

P5V

STB5V_M

IC9001

6

5

EEPROM

SDA

SCL

Q9704

Q9703

15

1

RUN/SS1

26

SW1

23

BG2

27

TG2

24

VIN

17

BG2

19

SW2

16

TG2

RUN/SS2

G2

S2

G1

S1

D2

D1

3.3V

Q9702

Q9701

P12V

1.5V

DC_DC CONV.

IC9702

D2

G1

S2

S1

G2

D1

2

1

4

IC9700

AVR 2.5V

3.3V

2.5V

NRST

DRV_RST

DATA POWER

FEEDBACK

DATA DRIVER

32M FLASH MEMORY

RESET

4

5

VOUT

VCC

IC9301

RESET

3.3V

SS PULSE

SCAN OUT

SC PULSE

3.3V

5V

IC9504

3.3V

5V

IC9503

48

51

UMH,UML,USH,USL,UEH,NUEL,ODED,ODEU

CL,CLK,SIU,SID,SCSU,CEL2,CPH,CEL,CBK,CSL,CSH,CML,CMH

IC9302

DDR SDRAM(64M)

DSHL,DSLL,DMHL,DMLL,DMHR

CLRU,LEU,PCU1,PCU2

Q9700

Q9901

6

DRVRST

Q9900

VD

HD

CLK4

10

CLK8

CLK1

11

7

14

CLK5

X1

1

20

X2

IC9200

PCK

OCK

DPCLK5

DPCLK2

D

ON/OFF

SW

Q9004

Q9001

OSD

P3V_SCL1

P3V_SDA1

P5V

FPD

A

T

A

0

FPD

A

T

A1

FPCLK

SCL

SDA

P3V_SCL2

P3V_SDA2

CONTROL

3.3V

3.3V

14

4

3.3V

1

DATA

6

2

IC9007

5

NCS

DCLK

ADSI

CONF_DONE

DATA0

NCS

NCE

ASDI0

NCONFIG

DCLK

TO K3

1

STB5V

STB5V_M

(PCD1)

(PCD2)

P5V

SDA

SCL

Control DATA

94

3.3V_DET

P12V_DET

93

95

P5V_DET

Q9023

Q9022

Q9021

Q9020

P5V

P12V

3.3V

DATA DRIVE

VCC

CTL

OUT

NOT USED

STB 5V

STB 5V 12

PROM (FPGA)

LEVEL CONVERTER

LEVEL CONVERTER

LEVEL CONVERTER

CLOCK GENE.

DIGITAL SIGNAL PROCESSOR

PlASMA AI

FORMAT CONVERTER,

SUB-FIELD PROCESSOR

FOR

FACTORY

USE

FOR

FACTORY

USE

D32

51

12

6

5

7

10

41

55

52

40

1

4

6

D31

8

27

36

52

29

30

31

34

5

R-UP

DATA R

(DATA R TIMING)

CLK1

CLK0

DATA DRIVE

5V DET

P5V

DRV-RST

DATA L

L-UP

CLK2

CLK3

DATA DRIVE

5V DET

P5V

DRV-RST

(DATA L TIMING)

TO C25

TO C24

Q9801

Q9800

(PCU1)

(PCU2)

P5V

P5V

P5V

P5V

DRVCLKD0-D3

DRVCLKU0-U3

36bit

(DA,DB,DC10-21)

(UA,UB,

33bit

33bit

(UA,UB,UC0-7,16-18)

UC8-15,

(DA,DB,DC0-9)

30bit

5V(P)

P5V

CLRD,LED,PCD1,PCD2

ODED,ODEU

19-21)

TH-50PX50U

D-Board Block Diagram

TH-50PX50U

D-Board Block Diagram

TH-37PX50U / TH-42PX50U / TH-50PX50U

157

Summary of Contents for TH37PX50U - 37" HD PLASMA TV

Page 24: ...7 Location of Lead Wiring 7 1 Lead of Wiring 1 TH 37PX50U 24 TH 37PX50U TH 42PX50U TH 50PX50U...

Page 25: ...7 2 Lead of Wiring 2 TH 37PX50U 25 TH 37PX50U TH 42PX50U TH 50PX50U...

Page 26: ...7 3 Lead of Wiring 3 TH 42PX50U 26 TH 37PX50U TH 42PX50U TH 50PX50U...

Page 27: ...7 4 Lead of Wiring 4 TH 42PX50U 27 TH 37PX50U TH 42PX50U TH 50PX50U...

Page 28: ...7 5 Lead of Wiring 5 TH 50PX50U 28 TH 37PX50U TH 42PX50U TH 50PX50U...

Page 29: ...7 6 Lead of Wiring 6 TH 50PX50U 29 TH 37PX50U TH 42PX50U TH 50PX50U...

Page 30: ...7 7 Lead of Wiring 7 30 TH 37PX50U TH 42PX50U TH 50PX50U...

Page 31: ...7 8 Lead of Wiring 8 TH 37PX50U 31 TH 37PX50U TH 42PX50U TH 50PX50U...

Page 32: ...7 9 Lead of Wiring 9 TH 42PX50U 32 TH 37PX50U TH 42PX50U TH 50PX50U...

Page 33: ...7 10 Lead of Wiring 10 TH 50PX50U 33 TH 37PX50U TH 42PX50U TH 50PX50U...

Page 37: ...8 4 No Picture 37 TH 37PX50U TH 42PX50U TH 50PX50U...

Page 40: ...9 4 Option 40 TH 37PX50U TH 42PX50U TH 50PX50U...

Page 44: ...10 4 Adjustment Volume Location 44 TH 37PX50U TH 42PX50U TH 50PX50U...

Page 45: ...10 5 Test Point Location 45 TH 37PX50U TH 42PX50U TH 50PX50U...

Page 108: ...TH 37PX50U TH 42PX50U TH 50PX50U 108...

Page 228: ...14 2 Pcaking Exploded Views 1 228 TH 37PX50U TH 42PX50U TH 50PX50U...

Page 229: ...14 3 Pcaking Exploded Views 2 229 TH 37PX50U TH 42PX50U TH 50PX50U...

Page 230: ...14 4 Pcaking Exploded Views 3 230 TH 37PX50U TH 42PX50U TH 50PX50U...