23

KX-TS2388RUB/KX-TS2388RUW/KX-TS2388CAB/KX-TS2388CAW/KX-TS2388UAB/KX-TS2388UAW

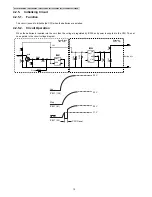

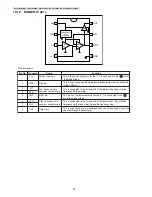

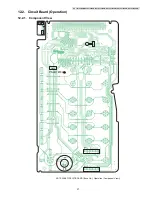

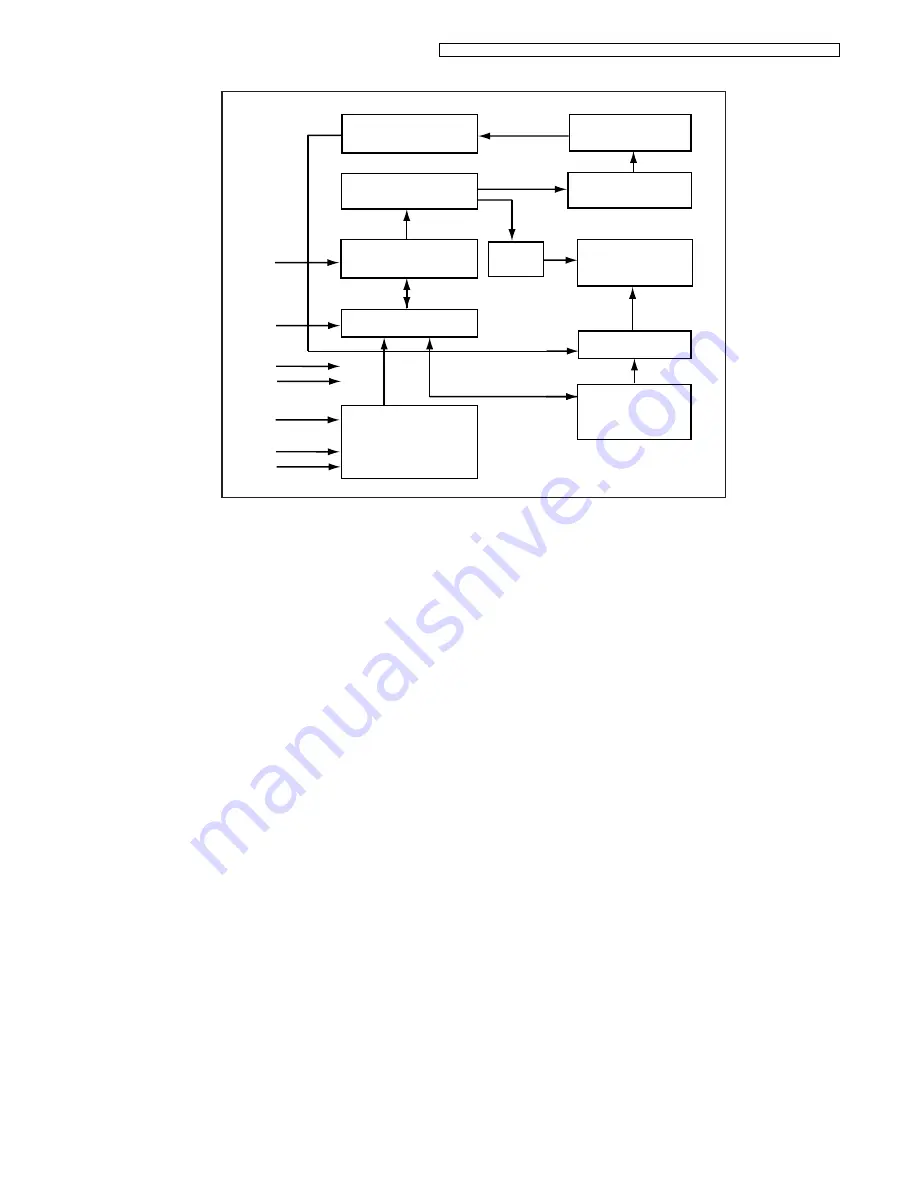

10.1.3. EEPROM (IC851)

1. SCL

SCL terminal is input terminal of Serial Clock to control transmit and receipt between Master and Slave.

2. SDA

SDA terminal is input terminal, to forward the address and the mutual data between Master Device and Slave Device the

mutual.

This terminal needs the pull-up resistance external because output circuit of SDA uses Open Drain.

3. A0, A1, A2

A0, A1, and A2 terminal is not used.

4. WP

WP terminal controls writing action. It is possible to do only reading action when high level input and it is possible to do read-

ing and writing action when low level input.

Do

u

t & ACK

(Open dr

a

in)

Control logic

S

en

s

e

a

mp

s

S

hift re

s

i

s

tor

Word

a

ddre

ss

bu

ffer

s

Col

u

mn decorder

s

S

t

a

rt/

S

top

logic

S

t

a

ge co

u

nter

s

&

S

l

a

ve

a

ddre

ss

Comp

a

r

a

tor

s

XDEC

Memory

a

rr

a

y

12

8

X 12

8

D

a

t

a

in

s

tor

a

ge

High volt

a

ge

gener

a

tor &

Timing control

S

DA

WP

Vcc

V

ss

S

CL

A1

A2

12

8