61

LTDVE4CH-20 | INSTRUCTIONS MANUAL

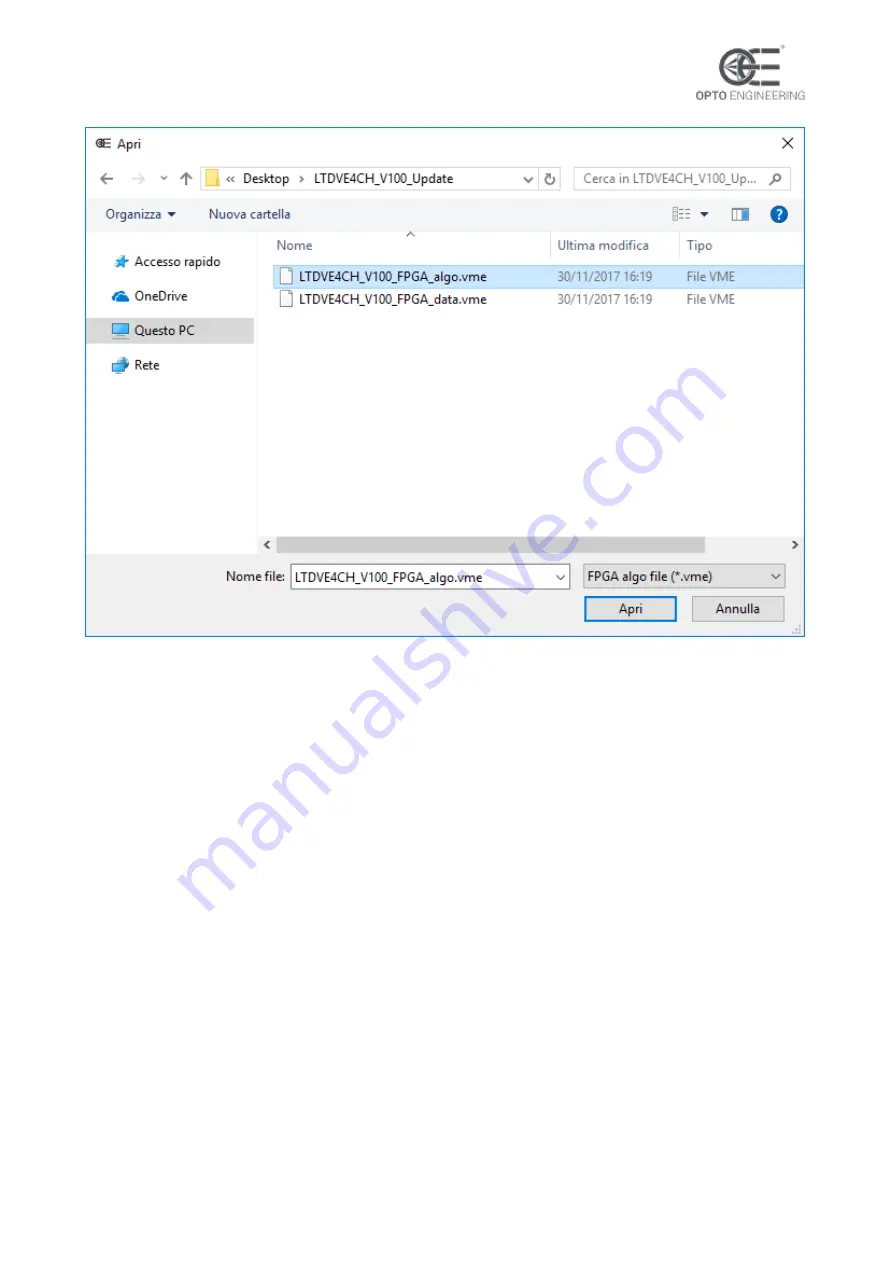

Figure 20: dialog used to locate the FPGA Algo firmware file

After the FPGA Algo file has been specified, the relative modal dialog is closed. The new modal

dialog of

Figure 21: dialog used to locate the FPGA Data firmware file

will then be displayed, asking

to specify the FPGA Data file.