CHAPTER 16 FLASH MEMORY

User’s Manual U18172EJ2V0UD

232

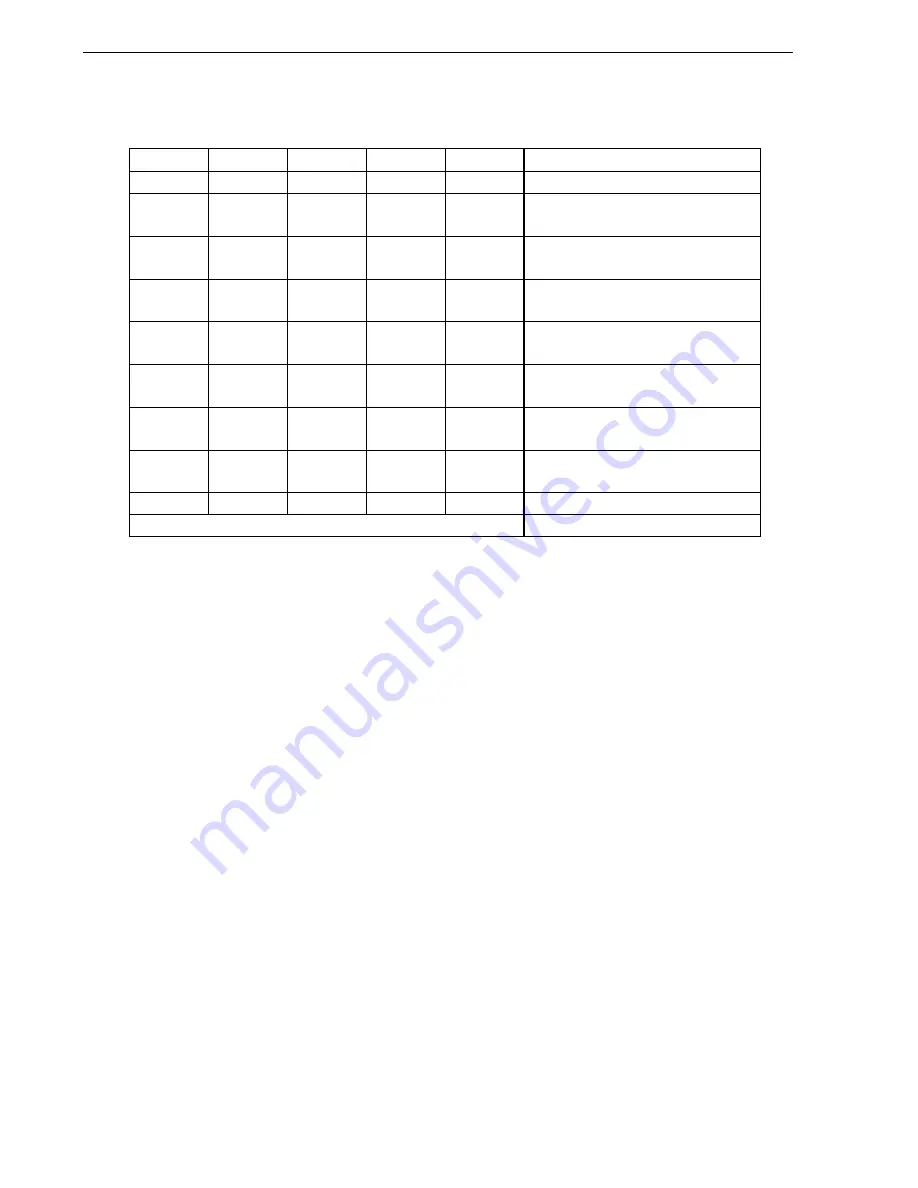

Figure 16-17. Format of Protect Byte (2/2)

•

µ

PD78F9202

PRSELF4 PRSELF3 PRSELF2 PRSELF1 PRSELF0

Status

0

1

0

0

0

Blocks 15 to 0 are protected.

0 1 0 0 1

Blocks 13 to 0 are protected.

Blocks 14 and 15 can be written or erased.

0 1 0 1 0

Blocks 11 to 0 are protected.

Blocks 12 to 15 can be written or erased.

0 1 0 1 1

Blocks 9 to 0 are protected.

Blocks 10 to 15 can be written or erased.

0 1 1 0 0

Blocks 7 to 0 are protected.

Blocks 8 to 15 can be written or erased.

0 1 1 0 1

Blocks 5 to 0 are protected.

Blocks 6 to 15 can be written or erased.

0 1 1 1 0

Blocks 3 to 0 are protected.

Blocks 4 to 15 can be written or erased.

0 1 1 1 1

Blocks 1 and 0 are protected.

Blocks 2 to 15 can be written or erased.

1

1

1

1

1

All blocks can be written or erased.

Other than above

Setting prohibited

16.8.4 Example of shifting normal mode to self programming mode

The operating mode must be shifted from normal mode to self programming mode before performing self

programming.

An example of shifting to self programming mode is explained below.

<1> Disable interrupts if the interrupt function is used (by setting the interrupt mask flag registers (MK0) to FFH

and executing the DI instruction).

<2> Clear FLCMD (FLCMD=00H).

<3> Clear the flash status register (PFS).

<4> Set self programming mode using a specific sequence.

Note

•

Write a specific value (A5H) to PFCMD.

•

Write 01H to FLPMC (writing in this step is invalid).

•

Write 0FEH (inverted value of 01H) to FLPMC (writing in this step is invalid).

•

Write 01H to FLPMC (writing in this step is valid).

<5> Execute NOP instruction and HALT instruction.

<6> Check the execution result of the specific sequence using bit 0 (FPRERR) of PFS.

Abnormal

→

<3>, normal

→

<7>

<7> Mode shift is completed.

Note

Set the CPU clock so that it is 1 MHz or more during self programming.

Caution Be sure to perform the series of operations described above using the user program at an

address where data is not erased or written.