Chapter 4

Signal Connections

©

National Instruments Corporation

4-25

PCI-4451/4452/4453/4454 User Manual

As an output, the GPCTR1_SOURCE monitors the actual clock connected

to general-purpose counter 1. This is true even if the source clock is

externally generated by another PFI signal. This output is set to

high-impedance at startup.

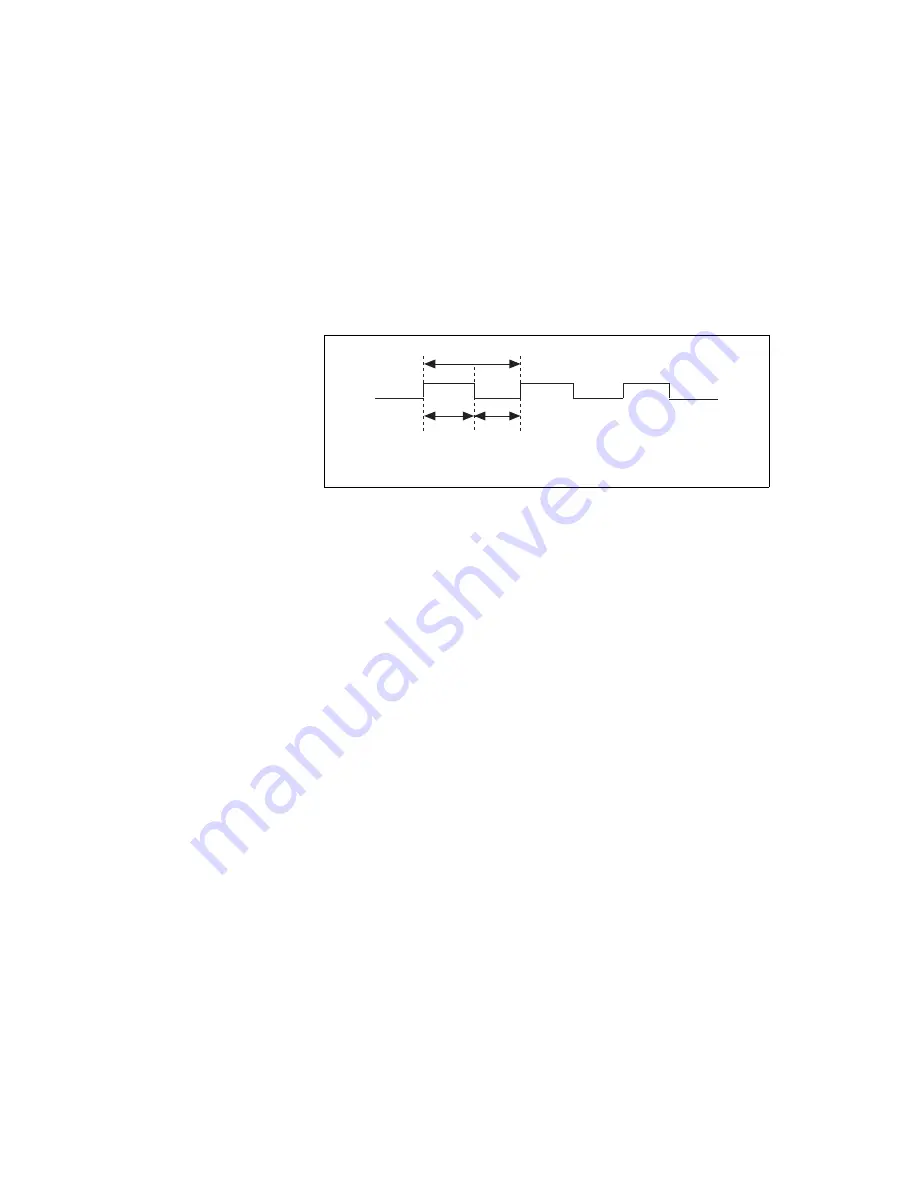

Figure 4-14 shows the timing requirements for the GPCTR1_SOURCE

signal.

Figure 4-14.

GPCTR1_SOURCE Signal Timing

The maximum allowed frequency is 20 MHz, with a minimum pulse width

of 23 ns high or low. There is no minimum frequency limitation.

The 20 MHz or 100 kHz timebase normally generates the

GPCTR1_SOURCE unless you select some external source.

GPCTR1_GATE Signal (PCI-4451/4452 Only)

Any PFI pin can receive as an input the GPCTR1_GATE signal, which is

available as an output on the PFI4/GPCTR1_GATE pin.

As an input, the GPCTR1_GATE signal is configured in edge-detection

mode. You can select any PFI pin as the source for GPCTR1_GATE and

configure the polarity selection for either rising or falling edge. You can use

the GATE signal in a variety of different applications to perform such

actions as starting and stopping the counter, generating interrupts, saving

the counter contents, and so on.

As an output, the GPCTR1_GATE signal monitors the actual GATE signal

connected to general-purpose counter 1. This is true even if the GATE is

externally generated by another PFI signal. This output is set to

high-impedance at startup.

t

p

t

w

t

w

t

p

t

w

= 50 ns minimum

= 23 ns minimum