8

2

1

Q

T

-

A

1

0

L

-

1

S

X

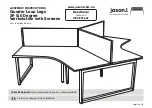

Block Diagram

¶

·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶

·

¶

·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶

·

¶

·

¶

·

¶

·

¶

·

¶

·

¶

·

¶

·

¶

·

¶

·

¶

·

¶

·

¶

·

¶

·

¶

·

¶

·

¶

·

¶

·

¶

·

¶

·

¶

·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

¶ ·

PCU_WAKE

PCU_GATE

PCU_CLK

PCU_VDD

PCU_VDDIO

TRST_N

TDI

TCK

TMS

PLL_AGND

DEBUG_N

PLL_AVDD

CLK

MODE[4:0]

RST_N

PCU

PLL

Core 4

Core 0

Core 1

Core 2

Core 5

Core 6

Core 7

Core 3

3

2

C

han

n

el

Ends

Boot ROM

JTAG

Switch

Switch

7 Synchronizers

6 Clock Blocks

10 Timers

4 Locks

1H

1G

1I

1J

1L

1N

1M

1O

1P

1D

1C

1E

1A

1K

X0D14

X0D15

X0D16

X0D18

X0D19

X0D20

X0D21

X0D01

X0D02

X0D03

X0D04

X0D05

X0D06

X0D07

X0D08

X0D09

X0D10

X0D11

X0D12

X0D13

X0D22

X0D23

X0D00

1F

1B

X0D17

X0D51

X0D52

X0D53

X0D54

X0D55

X0D57

X0D58

X0D61

X0D62

X0D63

X0D64

X0D65

X0D66

X0D69

X0D70

X0D49

X0D50

X0D68

X0D67

X0D26

X0D27

X0D29

X0D30

X0D31

X0D32

X0D33

X0D34

X0D35

X0D36

X0D37

X0D38

X0D39

X0D42

X0D43

X0D24

X0D25

X0D41

X0D40

X0D56

64KB SRAM

8KB OTP

Security Register

GND

OTP_VCC

VDD

VDDIO

XLD

XLC

XLB

XLA

Por

t

8

B

Por

t

8

A

Por

t

8

D

Por

t

8

C

Por

t

16

A

Por

t

3

2A

Por

t

16

B

X0D28

Por

t

4

B

Por

t

4

D

Por

t

4

F

4

A

4

A

4

C

4C

4

E

4

E

6

Summary of Contents for C 510

Page 1: ...NAD SERVICE MANUAL C510 C510 Direct Digital DAC Direct Digital DAC...

Page 18: ...1 MAIN BOARD 18 PCB LAYOUT Top Larer Bottom Layer...

Page 19: ...2 TRIGGER BOARD 19 Top Layer Bottom Layer 3 SMPS BOARD Top Layer Bottom Layer...

Page 20: ...4 FPP BOARD 20 Top Larer Bottom Layer...

Page 21: ...5 VFD AND ENCODE BOARD 21 Top Larer Bottom Layer...