MOTOROLA

Chapter 30. Serial Management Controllers

30-13

Part V. The Communications Processor Module

zeros, the number of which is the sum of the character length, plus the number of start,

parity, and stop bits. The SMC sends a programmable number of break characters

according to BRKCR and then reverts to idle or sends data if a

RESTART

TRANSMIT

is issued

before completion. When the break completes, the transmitter sends at least one idle

character before sending any data to guarantee recognition of a valid start bit.

30.3.8 Sending a Preamble

A preamble sequence provides a way to ensure that the line is idle before a new message

transfer begins. The length of the preamble sequence is constructed of consecutive ones that

are one character long. If the preamble bit in a BD is set, the SMC sends a preamble

sequence before sending that buffer. For 8 data bits, no parity, 1 stop bit, and 1 start bit, a

preamble of 10 ones would be sent before the Þrst character in the buffer. If no preamble

sequence is sent, data from two ready transmit buffers can be sent on the transmit pin with

no delay between them.

30.3.9 Handling Errors in the SMC UART Controller

The SMC UART controller reports character reception errors via the channel RxBD status

Þelds and the SMC event register (SMCE). Table 30-7 shows the possible UART receiving

errors. The SMC UART controller has no transmission errors.

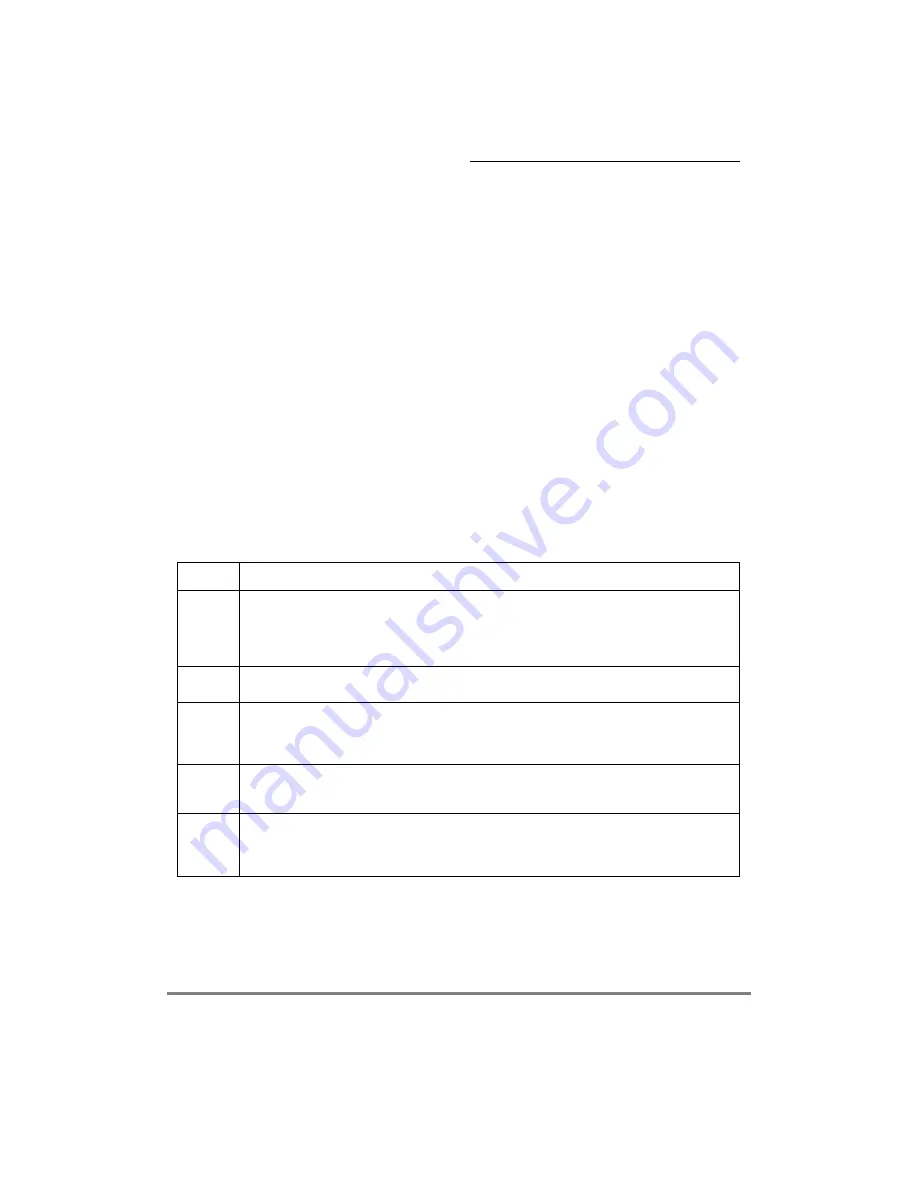

Table 30-7. SMC UART Errors

Error

Description

Overrun

The SMC maintains a two-character length FIFO for receiving data. Data is moved to the buffer after the

Þrst character is received into the FIFO; if a receiver FIFO overrun occurs, the channel writes the

received character into the internal FIFO. It then writes the character to the buffer, closes it, sets

RxBD[OV], and generates the RX interrupt if it is enabled. Reception then resumes as normal.

Overrun errors that occasionally occur when the line is idle can be ignored.

Parity

The channel writes the received character to the buffer, closes it, sets the PR bit in the BD, and

generates the RX interrupt if it is enabled. Reception then resumes as normal.

Idle

Sequence

Receive

An idle is found when a character of all ones is received, at which point the channel counts consecutive

idle characters. If the count reaches MAX_IDL, the buffer is closed and an RX interrupt is generated. If

no receive buffer is open, this does not generate an interrupt or any status information. The idle counter

is reset each time a character is received.

Framing

The SMC received a character with no stop bit. When it occurs, the channel writes the received

character to the buffer, closes the buffer, sets FR in the BD, and generates the RX interrupt if it is

enabled. When this error occurs, parity is not checked for the character.

Break

Sequence

The SMC receiver received an all-zero character with a framing error. The channel increments BRKEC,

generates a maskable BRK interrupt in SMCE, measures the length of the break sequence, and stores

this value in BRKLN. If the channel was processing a buffer when the break was received, the buffer is

closed with the BR bit in the RxBD set. The RX interrupt is generated if it is enabled.

Summary of Contents for MPC860 PowerQUICC

Page 3: ...MPC860UM AD 07 98 REV 1 MPC860 PowerQUICC ª UserÕs Manual ...

Page 36: ...xxxvi MPC860 PowerQUICC UserÕs Manual MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Page 78: ...I iv MPC860 PowerQUICC UserÕs Manual MOTOROLA Part I Overview ...

Page 88: ...1 10 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part I Overview ...

Page 114: ...3 16 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part I Overview ...

Page 226: ...8 32 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part II PowerPC Microprocessor Module ...

Page 262: ...9 36 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part II PowerPC Microprocessor Module ...

Page 274: ...III iv MPC860 PowerQUICC UserÕs Manual MOTOROLA Part III Configuration ...

Page 320: ...12 12 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part III Configuration ...

Page 325: ...MOTOROLA Part IV Hardware Interface IV v Part IV Hardware Interface ...

Page 326: ...IV vi MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Page 352: ...13 26 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Page 394: ...14 42 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Page 426: ...15 32 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Page 530: ...17 26 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Page 632: ...21 44 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Page 660: ...22 28 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Page 708: ...24 24 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Page 748: ...27 20 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Page 846: ...31 20 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Page 914: ...35 12 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Page 948: ...36 34 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Page 998: ...37 48 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part VI Debug and Test ...

Page 1016: ...A 10 MPC860 PowerQUICC UserÕs Manual MOTOROLA Appendixes ...

Page 1024: ...B 8 MPC860 PowerQUICC UserÕs Manual MOTOROLA Appendixes ...

Page 1030: ...C 6 MPC860 PowerQUICC UserÕs Manual MOTOROLA Appendixes ...

Page 1086: ...Glossary 12 MPC860 PowerQUICC UserÕs Manual MOTOROLA ...

Page 1106: ......