Universal Serial Bus (USB) Interface

Data Communication via Endpoints EP1 and EP2

USB08 Evaluation Board

Designer Reference Manual

MOTOROLA

Universal Serial Bus (USB) Interface

77

after 10 ms the host asks whether further data has to be fetched from

endpoint 1 or not.

NOTE:

In practice, the host uses only intervals of 2

n

ms, the demanded 10 ms

is then rounded to 8 ms.

The USB interrupt routine is called cyclically and branches to the handler

handleIN1. From there, data is taken from the ring buffer TxBuffer (if

available) and transferred into the USB endpoint 1 data registers

UE1D0–UE1D7. Subsequently, the number of bytes which should be

sent is registered in the fields TP1SIZ3–TP1SIZ0. If no data is in the

buffer, this number is registered as 0. The T1SEQ bit is inverted to switch

between DATA0 and DATA1 packets (data toggle). Finally, by setting

the bit TX1E in the USB control register 1 (UCR1), the transmission of

the data is enabled.

The operation mode selected here is based on a continuous data

stream. If there is no transmit data in the buffer, the device will send data

packets with zero byte contents. If this condition continues for a longer

time, sending of empty data packets means a waste of bus bandwidth.

If this turns out as critical, a change of the operation mode is

recommended. Alternatively, it is possible to disable TX1E, as long as

no data is present in the buffer. Then, the endpoint answers a polling

only with a NAK packet and does not occupy any additional bandwidth

by sending an empty data packet.

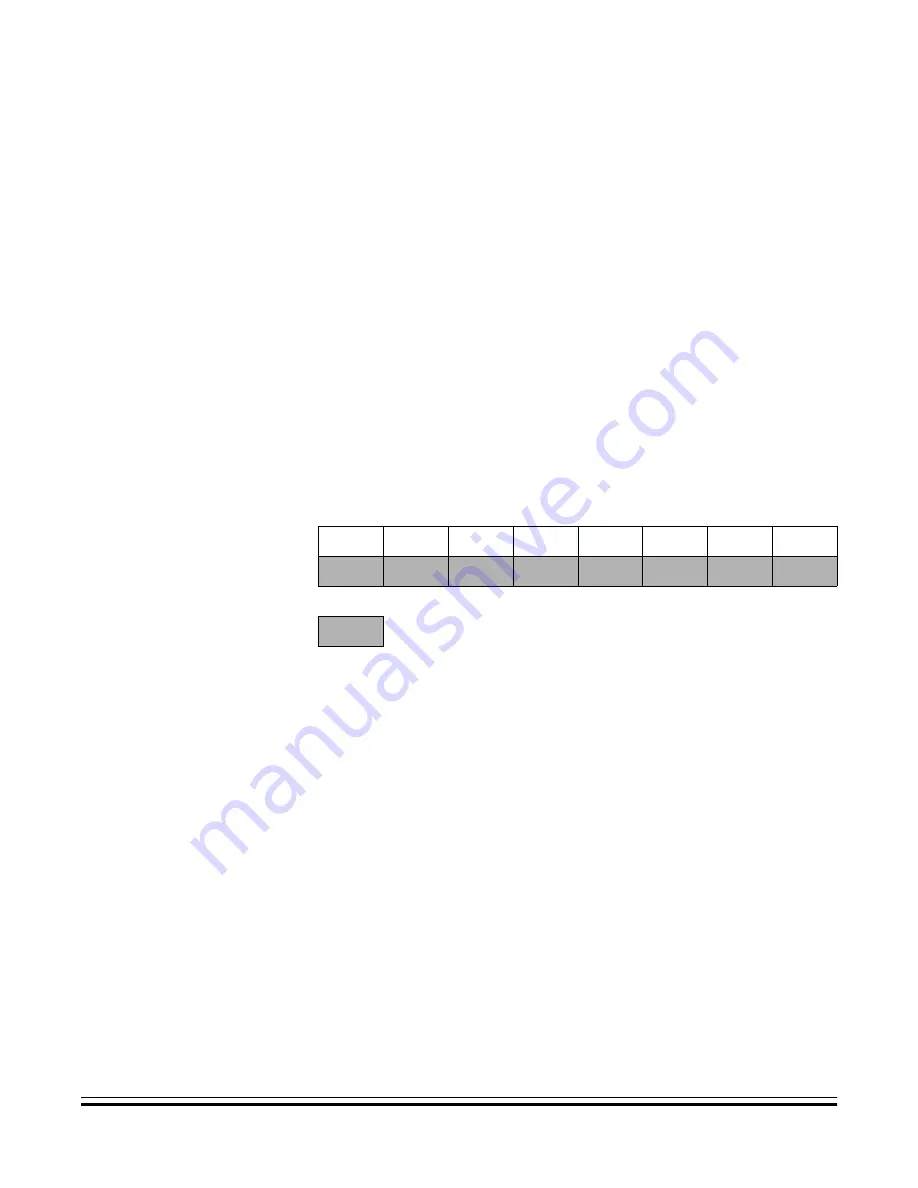

Bit 7

6

5

4

3

2

1

Bit 0

Read:

T1SEQ

STALL1

TX1E

FRESUM

TP1SIZ3

TP1SIZ2

TP1SIZ1

TP1SIZ0

Write:

Reset:

0

0

0

0

0

0

0

0

= Unimplemented

Figure 4-11. USB Control Register 1 (UCR1)