11-6

MC68838 USER’S MANUAL

MOTOROLA

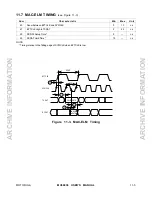

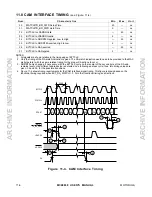

11.8 CAM INTERFACE TIMING

(see Figure 11-4)

Num

C h a r a c t e r i s t i c s

Min

M a x

U n i t

30

MATCH/TR_BR_FWD

Setup Time

40

—

ns

31

MATCH/TR_BR_FWD

Hold Time

5

—

ns

32

BYTCLK to LDADDR Valid

—

40

ns

33

BYTCLK to LDADDR Invalid

4

—

ns

34

BYTCLK to

ADDR16

Negated, Low to High

—

25

ns

35

BYTCLK to

ADDR16

Asserted, High to Low

2

—

ns

36

BYTCLK to DA Asserted

—

25

ns

37

BYTCLK to DA Negated

2

—

ns

NOTES:

1. All signals are shown relative to the rising edge of BYTCLK.

2. Only the timing of the DA match indication is given. The SA match indication would need to be provided to the MAC

six bytes later with the same relative timing for the proper SA actions to occur.

3.

ADDR16

only changes, if necessary, with the BYTCLK cycle on the receipt of the second byte of the DA and

remains level until a different address size is detected on a following address cycle; thus, two timing values are

given, 34 and 35, for the possible transitions.

4. Figure 11-4 shows timing requirements for the CAM interface signal timing. This figure is drawn based on the

functional timing required when EXT_DA_MATCH = 0. For other functional timing, see Section 9.

BYTCLK

LDADDR

SYMCLK

RCDAT

MATCH

80 NS

35

DA1

DA2

DA6

SA1

SA2

ADDR16

DA

32

37

FC

33

36

31

34

DA5

30

TR_BR_FWD

Figure 11-4. CAM Interface Timing

ARCHIVE INFORMA

TION

ARCHIVE INFORMA

TION

Summary of Contents for MC68838

Page 20: ...2 8 MC68838 USER S MANUAL MOTOROLA ARCHIVE INFORMATION ARCHIVE INFORMATION ...

Page 63: ...5 4 MC68838 USER S MANUAL MOTOROLA ARCHIVE INFORMATION ARCHIVE INFORMATION ...

Page 65: ...6 2 MC68838 USER S MANUAL MOTOROLA ARCHIVE INFORMATION ARCHIVE INFORMATION ...

Page 82: ...9 6 MC68838 USER S MANUAL MOTOROLA ARCHIVE INFORMATION ARCHIVE INFORMATION ...

Page 86: ...10 4 MC68838 USER S MANUAL MOTOROLA ARCHIVE INFORMATION ARCHIVE INFORMATION ...

Page 98: ...12 6 MC68838 USER S MANUAL MOTOROLA ARCHIVE INFORMATION ARCHIVE INFORMATION ...