68000 Motherboard User’s Manual

Rev. A

Page 8 of 54

numeral system is base 2, meaning that only these two digits are available. In base 2 the

significance of each digit’s place along a binary number differs by a factor of 2. When

written, binary numbers are expressed with a trailing subscript 2. Like in the base 10

system, the number 1

2

in binary represents a one. This is the ones place in the number,

2

0

. But binary 10

2

represents 2 or 2

1

, whereas in base 10 system 10

10

represents the

number ten or 10

1

. Binary 100

2

represents 4 or 2

2

. And 111

2

is a 7, 2

2

+2

1

+2

0

.

Another useful numeral system is base 16, known as hexadecimal. Hexadecimal simply

offers the advantage of grouping multiple binary digits together. Since the sixteen

possible combinations of four binary digits may be more concisely represented as a single

hexadecimal digit, hexadecimal is the preferred numeral system for its compactness.

Each hexadecimal digit represents four binary digits, and therefore two hexadecimal

digits represent a single 8-bit byte.

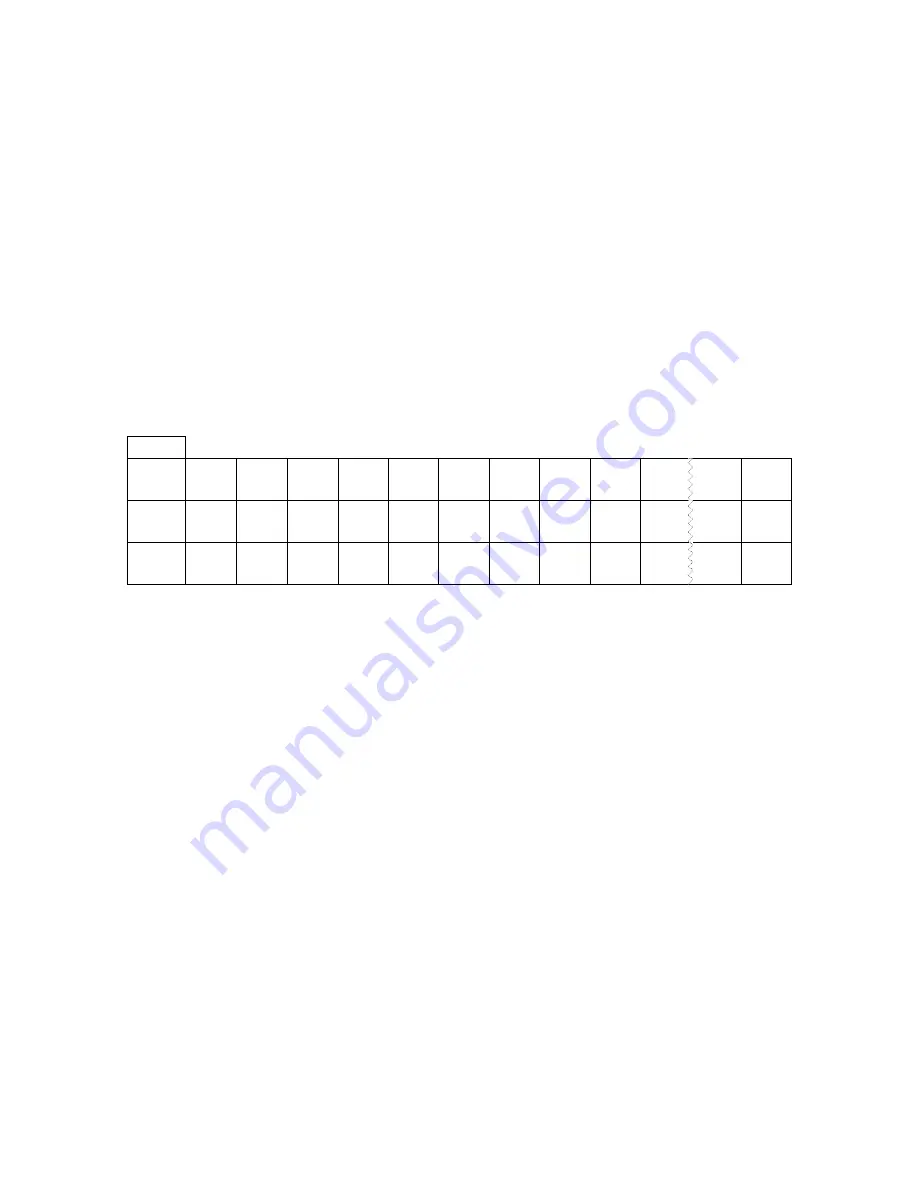

Table 1: Numeral Systems

Base

10

(Dec)

0

1

2

3

4

5

6

7

8

9

15

16

2

(Bin)

00000

2

00001

2

00010

2

00011

2

00100

2

00101

2

00110

2

00111

2

01000

2

01001

2

01111

2

10000

2

16

(Hex)

00

16

01

16

02

16

03

16

04

16

05

16

06

16

07

16

08

16

09

16

0F

16

10

16

As this relates to the computer, these binary digits physically correspond to the voltages

present on the signals within the computer. The digit 1 is typically represented by a high

voltage, while 0 is a low voltage. A succession of numbers over time in a digital system

appears as a signal waveform on the wire, with a separate parallel wire for each digit’s

place.

All data stored and processed in a computer can be thought of as numbers, encoded

through these voltage states. Whatever medium the data represents, it is a number

defined by parallel binary states to the computer. An image, for example, is defined

numerically as an array of values specifying how much red, green and blue to display at

each pixel location. Sound data numerically represents the amount to deflect a speaker

over time, which in turn creates corresponding sound waves. Text is defined numerically

by mapping the alphabet of possible characters to numerical codes. The message text

data is then broken into a string of characters, and the character at each position in that

string is defined by its numerical code. Using the ASCII coding standard as an example,

if 1 is added to the text data for the letter ‘A,’ it becomes a ‘B.’ If 32 is added to ‘A,’ it

becomes ‘a.’ To a computer, the world resolves to nothing more than numbers. These

numbers, though, have different meanings depending on which input or output device

they are associated. But within the computer, the numbers are simply electrical states of

the circuitry, carrying digital information.

Summary of Contents for MB68k-100

Page 1: ...Rev A Grant K c 2011 ...