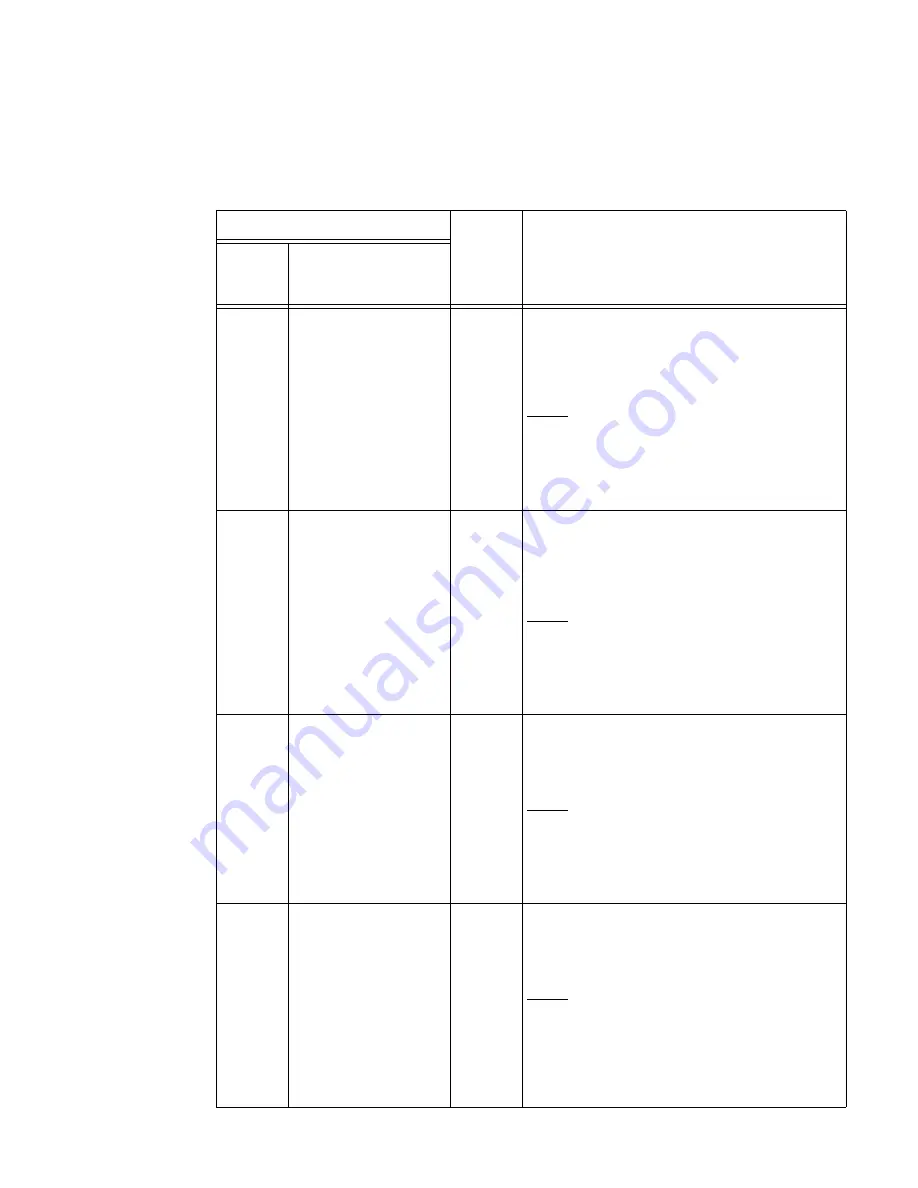

1-24

Communications Processor Module (CPM) Ports

PA15

FCC1: RXD5

UTOPIA

RXD2

MII

and

HDLC nibble

Input

Input

FCC1: UTOPIA Receive Data Bit 5

In the ATM UTOPIA interface supported by FCC1. The

MSC8101 inputs ATM cell octets (UTOPIA interface data)

on RXD[0–7]. RXD7 is the most significant bit. RXD0 is the

least significant bit. When no ATM data is available, idle

cells are inserted. A cell is 53 bytes. To support Multi-PHY

configurations, RXD[0–7] is tri-stated, enabled only when

RXENB is asserted.

FCC1: MII and HDLC Nibble Receive Data Bit 2

RXD[3–0] is supported by MII and HDLC nibble mode in

FCC1. RXD3 is the most significant bit. RXD0 is the least

significant bit.

PA14

FCC1: RXD4

UTOPIA

FCC1: RXD3

MII

and

HDLC nibble

Input

Input

FCC1: UTOPIA Receive Data Bit 4.

In the ATM UTOPIA interface supported by FCC1. The

MSC8101 inputs ATM cell octets (UTOPIA interface data)

on RXD[0–7]. RXD7 is the most significant bit. RXD0 is the

least significant bit. When no ATM data is available, idle

cells are inserted. A cell is 53 bytes. To support Multi-PHY

configurations, RXD[0–7] is tri-stated, enabled only when

RXENB is asserted.

FCC1: MII and HDLC Nibble Receive Data Bit 3

RXD[3–0] is supported by MII and HDLC nibble mode in

FCC1. RXD3 is the most significant bit. RXD0 is the least

significant bit.

PA13

FCC1: RXD3

UTOPIA

SDMA: MSNUM2

Input

Output

FCC1: UTOPIA Receive Data Bit 3

In the ATM UTOPIA interface supported by FCC1. The

MSC8101 inputs ATM cell octets (UTOPIA interface data)

on RXD[0–7]. RXD7 is the most significant bit. RXD0 is the

least significant bit. A cell is 53 bytes. To support Multi-PHY

configurations, RXD[0–7] is tri-stated, enabled only when

RXENB is asserted.

Module Serial Number Bit 2

MSNUM[0–4] is the sub-block code of the current peripheral

controller using SDMA. MSNUM5 indicates which section,

transmit (0) or receive (1), is active during the transfer.

PA12

FCC1: RXD2

UTOPIA

SDMA: MSNUM3

Input

Output

FCC1: UTOPIA Receive Data Bit 2

In the ATM UTOPIA interface supported by FCC1. The

MSC8101 inputs ATM cell octets (UTOPIA interface data)

on RXD[0–7]. RXD7 is the most significant bit. RXD0 is the

least significant bit. A cell is 53 bytes. To support Multi-PHY

configurations, RXD[0–7] is tri-stated, enabled only when

RXENB is asserted.

Module Serial Number Bit 3

MSNUM[0-4] of is the sub-block code of the current

peripheral controller using SDMA. MSNUM5 indicates

which section, transmit (0) or receive (1), is active during

the transfer.

Table 1-3. Port A Signals (Continued)

Name

Dedicated

I/O Data

Direction

Description

General-

Purpose

I/O

Peripheral Controller:

Dedicated Signal

Protocol