IGLOO2 FPGA Adaptive FIR Filter Demo

10

Revision 2

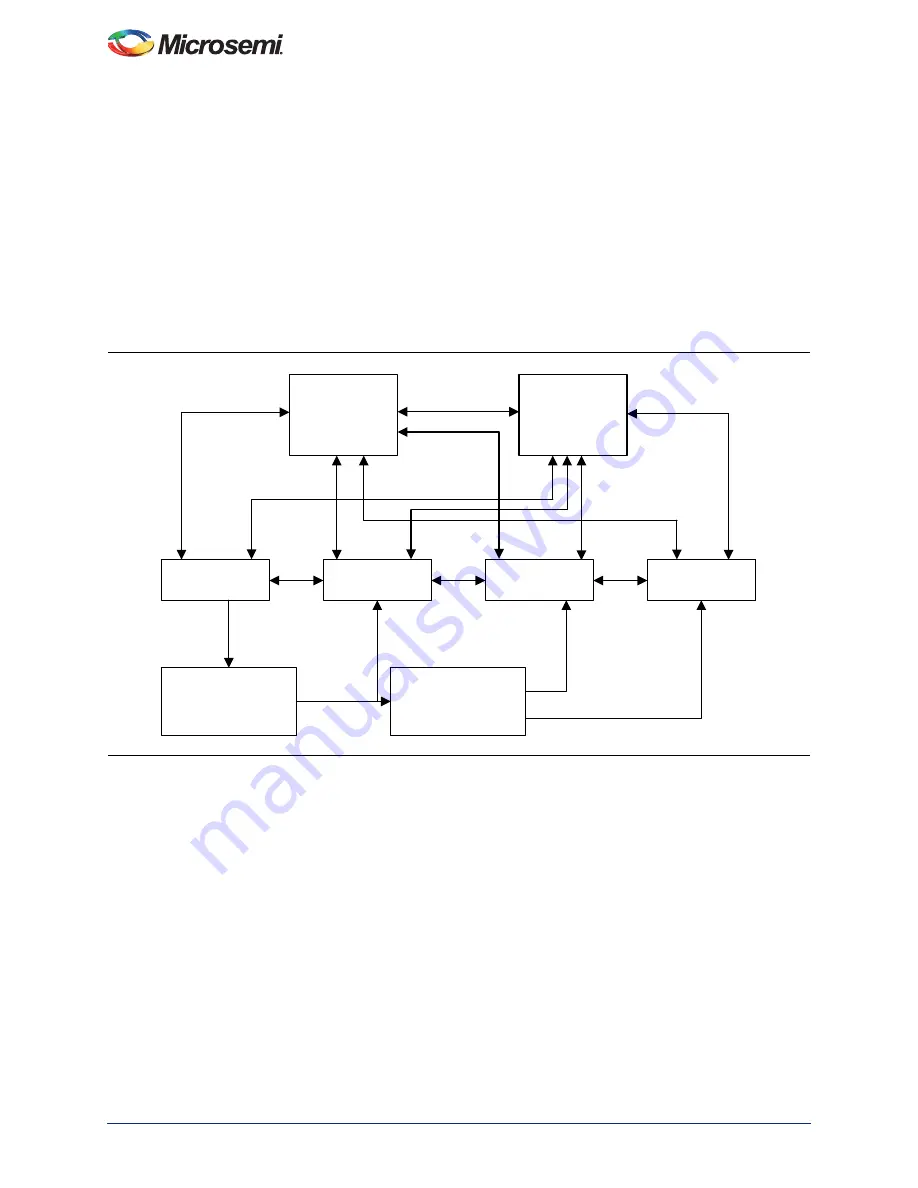

Demo Design Description

This demo design uses the following blocks:

•

"Data Handle Block"

(SmartDesign)

•

"Filter Control"

(user RTL)

•

"LMS_FIR_TOP"

(Smart Design)

•

"TPSRAM IP"

(IPcore)

•

"CoreFFT"

(IPcore)

•

"SYSRESET"

(IPcore)

•

"OSC"

(IPcore)

•

"CCC"

(IPcore)

•

"CoreUART"

(IP Core)

Data Handle Block

The Data handle block consists of a CoreUART IP and UART interface finite state machine to handle the

controls and operations between the Host PC (GUI interface) and fabric logic. It controls loading filter

input data to the corresponding input data buffer and then send and receive data from the Host PC.

Filter Control

Controls the FIR filter and FFT operations. It loads the filtered data to the corresponding output buffer

and moves the FFT output data to the corresponding output data buffer.

LMS_FIR_TOP

This is a SmartDesign block implemented in the fabric. It consists of the following blocks:

•

LMS_CONTROL_FSM

: This finite-state machine (FSM) is implemented in the RTL to provide the

control signals to the LMS_ALGO block.

•

LMS_ALGO

: This LMS algorithm is implemented in RTL to compute the error signal, correction

factor, filter coefficients, and to send the filter coefficients to the Core FIR filter.

Figure 6 •

Adaptive FIR Filter Demo Design Block Diagram

'DWD+DQGOH

)LOWHU&RQWURO

)60

),5,1%XIIHU

),5287%XIIHU

),55HDO%XIIHU

))7,PDJLQDU\

%XIIHU

/06B),5B723

&RUH))7

Superseded