MC80F0104/0204

Preliminary

60

Mar. 2005 Ver 0.2

13.6 PWM Mode

TheMC80F0104/0204 has high speed PWM (Pulse Width

Modulation) functions which shared with Timer1 or

Timer3.

In PWM mode, R10 / PWM1O or R11 / PWM3O pin out-

put up to a 10-bit resolution PWM output. These pins

should be configured as a PWM output by setting "1" bit

PWM1OE and PWM3OE in PSR0 register.

The period of the PWM1 output is determined by the

T1PPR (T1 PWM Period Register) and T1PWHR[3:2]

(bit3,2 of T1 PWM High Register) and the duty of the

PWM output is determined by the T1PDR (T1 PWM Duty

Register) and T3PWHR[1:0] (bit1,0 of T1 PWM High

Register).

The period of the PWM3 output is determined by the

T3PPR (T3 PWM Period Register) and T3PWHR[3:2]

(bit3,2 of T3 PWM High Register) and the duty of the

PWM output is determined by the T3PDR (T3 PWM Duty

Register) and T3PWHR[1:0] (bit1,0 of T3 PWM High

Register).

The user writes the lower 8-bit period value to the

T1(3)PPR( and the higher 2-bit period value to the

T1(3)PWHR[3:2]. And writes duty value to the T1(3)PDR

and the T1(3)PWHR[1:0] same way.

The T1(3)PDR is configured as a double buffering for

glitchless PWM output. In Figure 13-18 , the duty data is

transferred from the master to the slave when the period

data matched to the counted value. (i.e. at the beginning of

next duty cycle)

PWM1(3) Period = [PWM1(3)HR[3:2]T(2)3PPR] X

Source Clock

PWM1(3) Duty = [PWM3HR[1:0]T3PDR] X Source

Clock

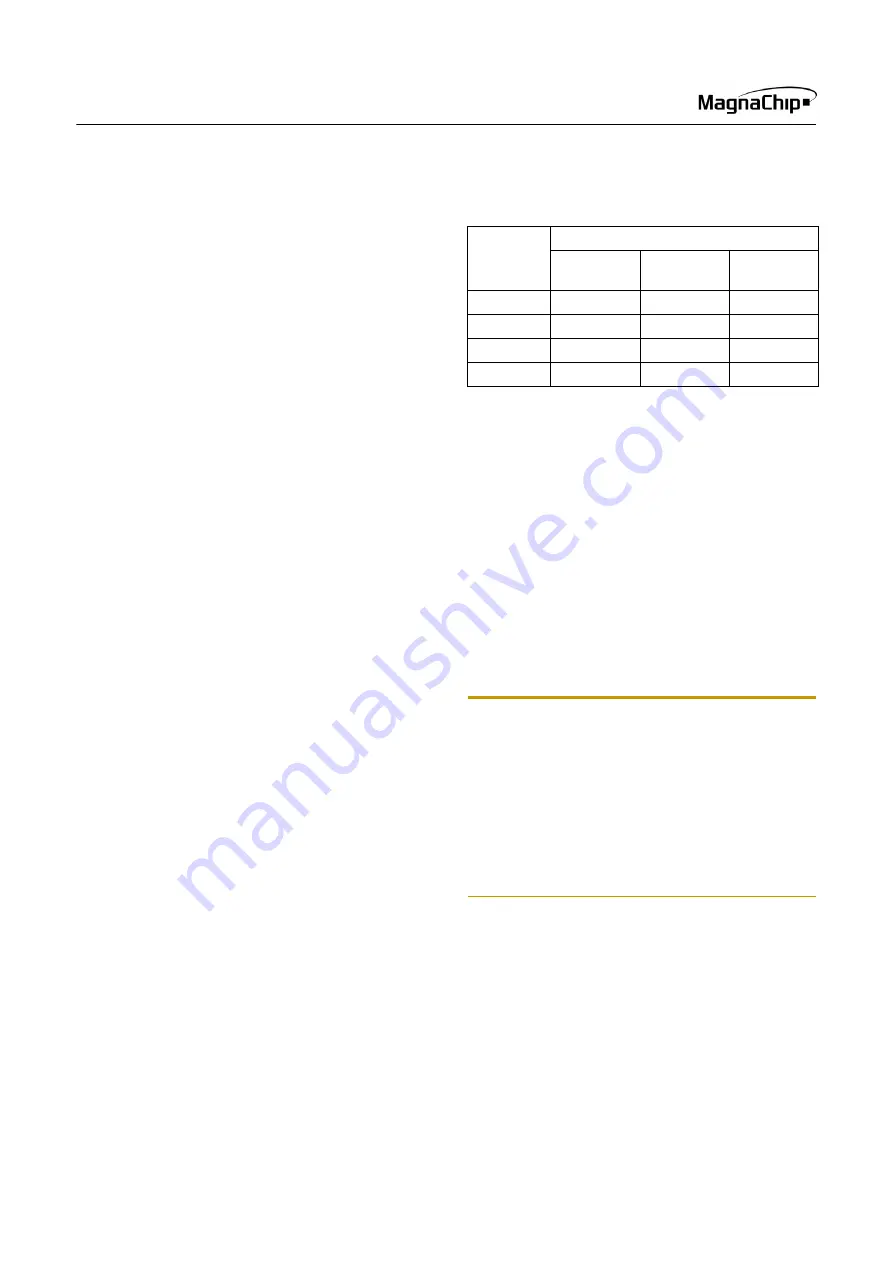

The relation of frequency and resolution is in inverse pro-

portion. Table 13-3 shows the relation of PWM frequency

vs. resolution.

If it needed more higher frequency of PWM, it should be

reduced resolution.

The bit POL of TM1 or TM3 decides the polarity of duty

cycle.

If the duty value is set same to the period value, the PWM

output is determined by the bit POL (1: High, 0: Low). And

if the duty value is set to "00

H

", the PWM output is deter-

mined by the bit POL (1: Low, 0: High).

It can be changed duty value when the PWM output. How-

ever the changed duty value is output after the current pe-

riod is over. And it can be maintained the duty value at

present output when changed only period value shown as

Figure 13-20 . As it were, the absolute duty time is not

changed in varying frequency. But the changed period val-

ue must greater than the duty value.

Note:

If changing the Timer1 to PWM function, it should be stop

the timer clock firstly, and then set period and duty register value.

If user writes register values while timer is in operation, these reg-

ister could be set with certain values.

Ex) Sample Program @4MHz 2uS

LDM TM1,#1010_1000b ; Set Clock & PWM3E

LDM T1PPR,#199 ; Period :400uS=2uSX(199+1)

LDM T1PDR,#99 ; Duty:200uS=2uSX(99+1)

LDM PWM1HR,00H

LDM TM1,#1010_1011b ; Start timer1

Resolution

Frequency

T1CK[1:0]

= 00(250nS)

T1CK[1:0]

= 01(500nS)

T1CK[1:0]

= 10(2uS)

10-bit

3.9kHz

0.98kHz

0.49kHz

9-bit

7.8kHz

1.95kHz

0.97kHz

8-bit

15.6kHz

3.90kHz

1.95kHz

7-bit

31.2kHz

7.81kHz

3.90kHz

Table 13-3 PWM Frequency vs. Resolution at 4MHz

Summary of Contents for MC80C0104

Page 108: ...MC80F0104 0204 Preliminary 104 Mar 2005 Ver 0 2 25 Emulator EVA Board Setting...

Page 115: ...APPENDIX...

Page 116: ......

Page 124: ...viii Mar 2005 Ver 0 2 MC80F0104 0204 Preliminary...