3-37

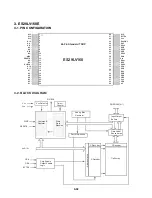

5. IP9009

5-1. PIN CONFIGURATION

28

27

26

25

24

23

22

21

20

19

18

17

16

15

1

2

3

4

5

6

7

8

9

10

11

12

13

14

BIAS

REBadj REOadj

Reset

Vdet

IN4

IN3

PGND

MUTE

PVCC2

GND

VO4-

VO4+

VO3-

VO3+

FWD

REV

CTL

PS

IN1

IN2

SVCC

PGND

PVCC1

VOL-

VOL+

VO2-

VO2+

VO1-

VO1+

I P 9 0 0 9

5-2. BLOCK DIAGRAM

28

27

26

25

24

23

22

21

20

19

18

17

16

15

BIAS

REBadj REOadj

Reset

Vdet

IN4

IN3

PGND

MUTE

PVCC2

GND

VO4-

VO4+

VO3-

VO3+

1

2

3

4

5

6

7

8

9

10

11

12

13

14

FWD

REV

CTL

PS

IN1

IN2

SVCC

PGND

PVCC1

VOL-

VOL+

VO2-

VO2+

VO1-

VO1+

Reset

MUTE

TSD

LEVEL SHIFT

-

+

LEVEL SHIFT

-

+

LEVEL SHIFT

-

+

LEVEL SHIFT

-

+

LEVEL SHIFT

-

+

P/S

MSC

SWITCH

D

D

D

D

D

D

D

D

D

D

45K

45K

45K

45K

10K

10K

10K

10K

5-3. PIN DESCRIPTION

No SYMBOL

I/O

SYMBOL

1

FWD

I

Loading motor forward input

2

REV

I

Loading motor reverse input

3

CTL

I

Loading motor speed control

4 PS I

Power

save

5 IN1 I

CH1

input

6 IN2 I

CH2

input

7

SVCC

-

Signal power supply

8

PVCC1

-

Power supply 1

9

VOL-

O

Loading driver output(-)

10

VOL+

O

Loading driver )

11

VO2-

O

CH2 driver output(-)

12

VO2+

O

CH2 driver )

13

VO1-

O

CH1 driver output(-)

14

VO1+

O

CH1 driver )

No SYMBOL

I/O

SYMBOL

15

VO4+

O

CH4 driver )

16

VO4-

O

CH4 driver output(-)

17

VO3+

O

CH3 driver )

18

VO3-

O

CH3 driver output(-)

19 GND -

Ground

20

PVCC2

-

Power supply 2

21 MUTE I Mute

22 IN3 I

CH3

input

23 IN4 I

CH4

input

24

Vdet

I

Reset controller input

25

Reset

O

Reset controller output

26

REOadj

O

Adjustable regulator feedback

27

REBadj

O

Adjustable regulator control

28 BIAS I Bias

Summary of Contents for MBD-D102X

Page 7: ...1 6 MEMO ...

Page 10: ...2 5 3 SPEAKER SECTION MBS D102V 750 751 752 754 755 757 A70A 758 A70 757A 759 756 753 ...

Page 35: ...3 24 4 FOCUS WAVEFORM 1 FDO 2 F 3 F INSERT CD INSERT DVD 1 FDO 2 F 3 F ...

Page 37: ...3 26 7 TRACKING SIGNAL 1 Tro 2 Tr 3 Tr 8 RF WAVEFORM ...

Page 38: ...3 27 9 DISK TYPE JUGEMENT WAVEFORM 1 F 2 FDO 3 SVRRF DVD CD ...

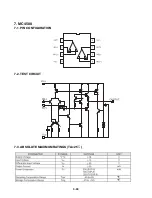

Page 50: ...3 39 7 MC4580 7 1 PIN CONFIGURATION 7 2 TEST CIRCUIT 7 3 ABSOLUTE MAXIMUM RATINGS TA 25 ...

Page 60: ...3 49 3 50 WIRING DIAGRAM ...

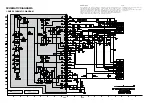

Page 62: ...3 53 3 54 2 MAIN FRONT BLOCK DIAGRAM ...

Page 64: ...3 57 3 58 2 MAIN INTERFACE PWM SCHEMATIC DIAGRAM ...

Page 65: ...3 59 3 60 3 MPEG SCHEMATIC DIAGRAM ...

Page 66: ...3 61 3 62 4 SERVO SCHEMATIC DIAGRAM ...

Page 67: ...3 63 3 64 5 INTERFACE SCHEMATIC DIAGRAM ...

Page 68: ...3 65 3 66 6 FRONT SCHEMATIC DIAGRAM ...

Page 69: ...3 67 3 68 7 FRONT MIC SCHEMATIC DIAGRAM ...

Page 70: ...3 69 3 70 8 IPOD 1 SCHEMATIC DIAGRAM OPTION ...

Page 71: ...3 71 3 72 9 IPOD 2 SCHEMATIC DIAGRAM OPTION ...

Page 72: ...3 73 3 74 10 2 CHANNEL AMP SCHEMATIC DIAGRAM ...

Page 73: ...3 75 3 76 11 BLUTHOOTH MODULE SCHEMATIC DIAGRAM OPTION ...

Page 75: ...3 79 3 80 1 MAIN P C BOARD TOP VIEW PRINTED CIRCUIT BOARD DIAGRAMS ...

Page 76: ...3 81 3 82 MAIN P C BOARD BOTTOM VIEW ...

Page 77: ...3 83 3 84 2 FRONT P C BOARD TOP VIEW BOTTOM VIEW ...

Page 78: ...3 85 3 86 3 SMPS P C BOARD TOP VIEW BOTTOM VIEW ...