37

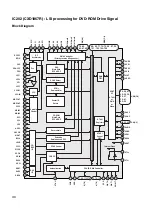

IC701 (CXD3030R) : DSP

Generates Error Signal and return to the Servo by the Signal from RF Amplifier IC.

70

138

139 40

82

94

102

84

85

86

41

96

100

13

104

103

34

79

47

49

50

81

27

60

77

91

62

61

103

12

93

95

21

33

35

36

56

58

98

57

14

5

2

63

99

97

10

65

111

134

135

143

142

116

83

3

4

39

38

37

44

45

43

42

Clock

Generator

32K RAM

Digital PLL

Vari-Pitch

double

speed

EFM

Demodulator

Sync

D/A

protector

Address

generator

8Fs Digital Filter

+

1 bit DAC

Priority

encoder

Timing

CLV

processor

Servo

auto

Digital Out

Generator1

Timing

Generator2

Noise

Shaper

18~times

oversampling

filter

P~W

Subcode

Subcode Q

processor

processor

CPU

interface

Servo

Interface

SERVO DSP

DAC

O

p

Amp

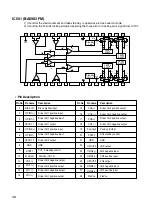

FOCUS SERVO

TRACKINGSERVO

FOCUS

SLED

TRACKING

SLED SERVO

O

p

Amp

AnaSw

A/D

CONVERTER

MIRR

DFCT

FOK

Peak

detector

Error

corrector

data

processor

Serial/parallel

processor

Register

XTLO

BSSD

XTLI

VPCO1

XTSL

PCMDI

BCKI

LRCKI

DTSO

XWO

RMUTO

LMUTO

Error Rate

Counter

sequencer

OSC

MCKO

V16M

VCKI

FSTIO

C4M

C16M

VCTL

PCO

VCOI

FILI

FILO

CLTV

RFAC

ASYI

ASYO

ASYE

WFCK

SCOR

10

GRSCOR

EXCK

SBSO

SQCK

SQSO

MDS

MDP

MON

FSW

PWMI

TEST

TEST2

TEST3

XRST

ADIO

RFDC

CE

TE

SE

FE

VC

SAO

TAO

FAO

COUT

SENS

DATA

DOUT

MUTE

PSSL

PWM1P

PWM1N

PWM2P

PWM2N

PCMD48

BCK48

PCMD64

LRCK48

BCK64

LRCK64

GTOP. XUGF. XPLCK

GFS. RFCK. C2PO. XRAOF

MNT0~3

MD2

CLOK

XLAT

MIRR

DFCT

FOK

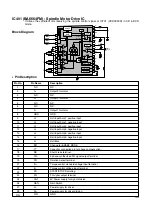

SIGNAL PROCESSOR BLOCK

SERVO BLOCK

DAC BLOCK

87

88

89

113

118

75 76 74

80 8

9

8

MUX

*

* :

Asymmetry

Correction

121, 123, 25, 59

28, 126, 128

16~19

Block Diagram