3-35

3-36

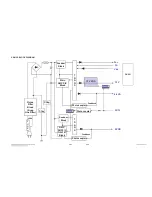

BLOCK DIAGRAMS

1. SYSTEM BLOCK DIAGRAM

DSP IC501

MLC3730

176PIN BGA

IC201

CS5346

M

P/UP

IC408

AM5890

Motor

Drive

SPDO/SLDO/FOD/TRD

OP_SW,CL_SW

A,B,C,D,E,F/ PD

MOT_MUTE/CLOSE/OPEN

SPIN ±

SLED±

F±/TR±

LOAD ±

IC407

LC78615E

(New)

LD/VREF

IM(CMS-S79RFVC6)

CD_16M

CD_MCK/RW/DIN_OUT/BUSY

CD_RESB

CD_BCK/CD_LRCK/CD_DATA

ADC_RST/CLK/DAT

TUNER_L/R

TUNER

AUX

AUX_L/R

A

PTB_L/R

Portable

ADC_DATA

REMOCON/KEY

VFD

VFD_STB/CLK/DO

IC301

ABOV

TUNER

TUNER_L/R

TUNER_RST/CE/DAT/CLK

A

PWM DAT/CLK

IC601

TAS5548

PWM

FL±

FR ±

FL

AMP_PDN

AMP_OTW/SD/CLIP/AMP PROTECT

FR

IC701

AMP IC

TAS5624LA

SW

IC702

AMP IC

TAS5624LA

SW

PWM_RST

DAC_BCK/LRCK/DATA

PWM_MUTE

DAC_BCK/DAC_LRCK/DAC_MCLK

DRM_SEL/DRM_CKE/DRM_RAS

DRM_CLK/DRM_CAS/DRM_WEN

D0~D15/A0~A11/A13~A16

SF_DI/DO

SF_CS/CLK(SPI)

USB1_D±

IC511

IPOD 2.0C

CP_RESET/SCL/SDA

IC502 SDRAM

IC503 FLASH

W25Q16FVSSIG

8 MB

2 MB

BT4.0(New)

RX/TX/RTS/CTS/RST/SDA/SCL

USB2_D±

PTB_SENSE

SF_DI/DO

SF_CS/CLK(SPI)

IC504 FLASH

W25Q80DVSSIG

1 MB

Interrupt

controller

CDROM x8 speed

Decoder

NAND Controller

within BCH codec

14bits ECC

GDMA 3ch

ADC (12bit*5ch)

Timer, Watchdog

GPIO (72 Max)

SPI 4ch (Max)

RTC & Wake up

UART 4ch (Max)

I2C 2ch

SDHC-SDIO 4ch (Max)

USB 2.0 OTG

SRAM (10K)

Main Processor

Audio DSP-0

GDMA 2ch

I2S (7.1ch)

SPDIF (Rx, Tx)

ADPCM

PLL

Clock Controller

Reset Controller

Test Controller

Audio DSP-1

USB 1.1

Host/Device

ARM

926EJS

16KB

I-Cache

16KB

D-Cache

400Mhz

DSP

133Mhz

SRAM29KB

I-Cache 8KB

D-Cache 8KB

DSP

133Mhz

SRAM29KB

I-Cache 8KB

D-Cache 8KB

Boot ROM (20KB)

SDRAM

Controller

Summary of Contents for CM4550

Page 13: ...2 2 ...

Page 17: ...A60 4 SPEAKER SECTION 4 1 FRONT SPEAKER CMS4550F ...

Page 18: ...2 9 A90 4 2 SUBWOOFER SPEAKER CMS4550W ...

Page 19: ...2 10 ...

Page 50: ...4 USB 13 USB_5 V D D 14 3 31 IC501 PIN A8 IC501 PIN A7 ...

Page 51: ...3 32 ...

Page 66: ...3 61 3 62 2 MAIN P C BOARD TOP VIEW BOTTOM VIEW ...

Page 67: ...3 63 3 64 3 FRONT P C BOARD TOP VIEW BOTTOM VIEW ...