TK-U100

(

V

)

13

CIRCUIT DESCRIPTION /

电路说明

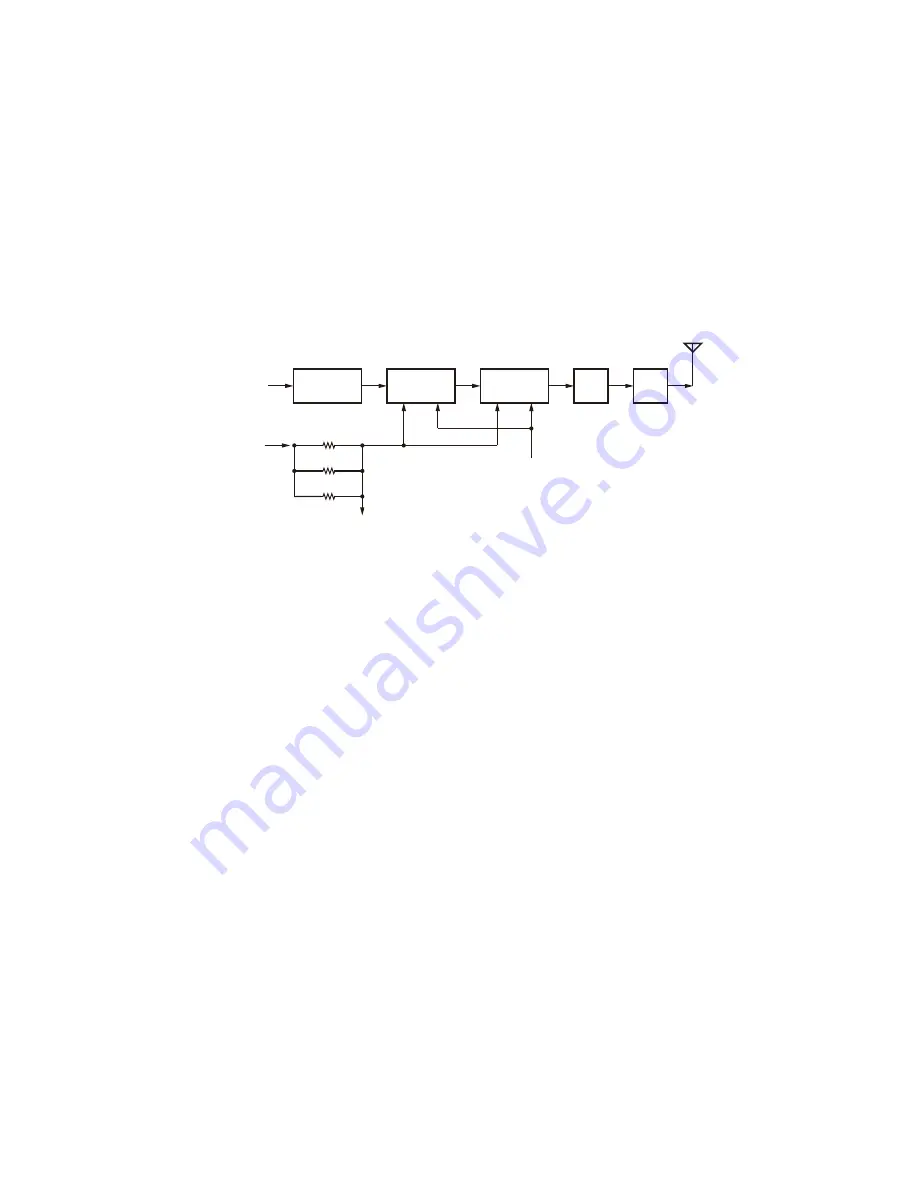

3-2. Driver and Final Amplifi er Circuit

The signal from the T/R switch (D100 is on) is amplifi ed

by the pre-drive amplifi er (Q100) to 30mW.

The output of the pre-drive amplifi er is amplifi ed by the

drive amplifi er (Q101) and the RF fi nal amplifi er (Q102) to

5.0W (1W when the power is low).

The drive amplifi er and the RF fi nal amplifi er consist of

two MOS FET stages.

The output of the RF final amplifier is then passed

through the harmonic fi lter (LPF) and antenna switch (D101

and D102) and is applied to the antenna terminal.

3-2. 驱动器和末级放大器电路

来自于 T/R 开关 (D100 ON) 的信号被预驱动放大器 (Q100)

放大到 30mW。

预驱动放大器的输出被驱动放大器 ( Q101) 和射频末级放大

器 (Q102) 放大到 5.0W( 当低功率时为 1W)。

驱动放大器和 RF 末级放大器由 2 个 MOS FET 构成。

射频末级放大器的输出通过谐波滤波器 ( L P F ) 和天线开关

(D101 和 D102) 并且送到天线终端。

Fig. 4 Drive and fi nal amplifi er circuit /

图 4 驱动及末级放大器电路

ANT

RF FINAL

AMP

ANT

SW

LPF

From

T/R SW

(D100)

D101,102

+B

POWC

Q102

DRIVE

AMP

Q101

VDD

VG

Pre-DRIVE

AMP

Q100

R121

R122

R123

CURDET

4. Frequency Synthesizer Circuit

4-1. Frequency Synthesizer

The frequency synthesizer consists of the TCXO (X1),

VCO, PLL IC (IC1) and buffer amplifi ers.

The TCXO generates 19.2MHz. The frequency stability is

5.0ppm within the temperature range of –30 to +60°C.

The frequency tuning and modulation of the TCXO are

done to apply a voltage to pin 1 of the TCXO. The output of

the TCXO is applied to pin 1 of the PLL IC.

The VCO consists of 1VCO and covers a dual range of the

144.00~174.00MHz and the 182.85~212.85MHz. The VCO

generates 182.85~212.85MHz for providing to the fi rst local

signal in receive.

The PLL IC consists of a prescaler, reference divider,

phase comparator, charge pump (The frequency step of the

PLL circuit is 5 or 6.25kHz).

PLL data is output from DATA (pin 19), CLOCK (pin 18)

and PLDL (pin 20) of the MCU (IC400). The data are input to

the PLL IC when the channel is changed or when transmis-

sion is changed to reception and vice versa. A PLL lock con-

dition is always monitored by the pin 22 (PLUL) of the MCU.

When the PLL is unlocked, the PLUL goes low.

4. 频率合成器电路

4-1. 频率合成器

频率合成器由 TCXO(X1)、VCO、PLL IC(IC1) 和缓冲放大器

组成。

TCXO 产生 19.2MHz 的频率。在温度为 -30 ~ +60℃的范围内,

频率的稳定性为 5.0ppm。进行频率调谐和 TCXO 调制,以便给

TCXO 的针脚 1 提供电压。TCXO 的输出加在 PLL IC 的针脚 1 上。

V C O 由 1V C O 组 成, 并 且 覆 盖 了 144.00 ~ 174.00M H z 和

182.85 ~ 212.85MHz 双波段。VCO 产生 182.85 ~ 212.85MHz

的频率,以提供接收的第一个本振信号。

P L L I C 由预计数器、基准除法器、相位比较器、电荷泵组

成 (PLL 电路的频率步长为 5kHz 或 6.25kHz)。

PLL 数据从 MCU(IC400) 的 DATA( 针脚 19),CLOCK( 针脚

18) 和 PLDL( 针脚 20) 输出。当信道改变时,或当由发射

变为接收或由接收变为发射时,数据输入 P L L I C。P L L 的

锁定条件总是由 MCU 的针脚 22(PLUL) 监控。当 PLL 失锁时,

PLUL 为低电位。

Summary of Contents for TK-U100

Page 44: ...TK U100 V 40 MEMO 笔记 ...