2-24(No.YA707<Rev.001>)

(No.YA707<Rev.001>)2-23

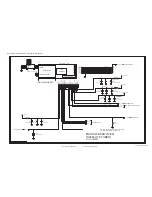

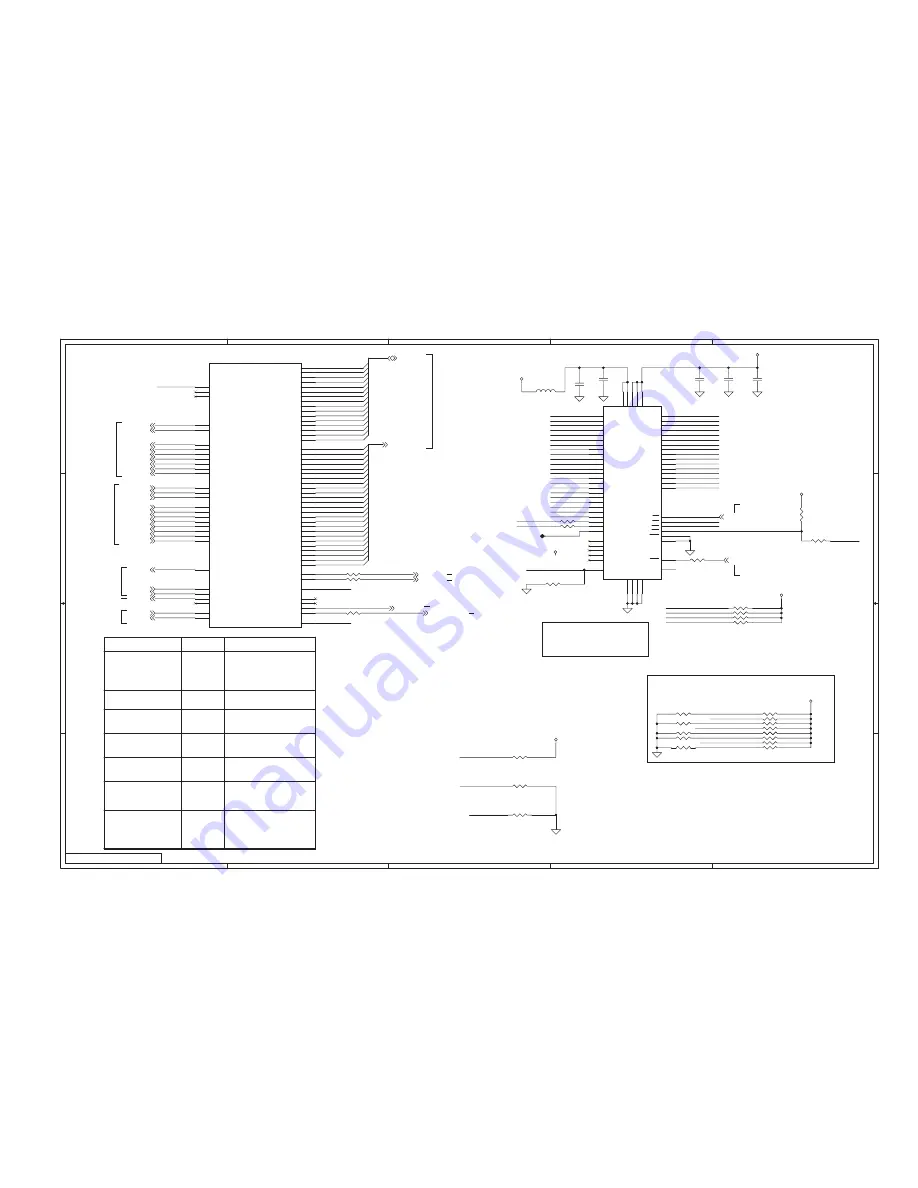

MAIN PWB ASS'Y(8/46)

[Flash and CI Interface]

HU-71100006

hb1_main_0612_6/48_0.0

5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

HOST_D0

HOST_D1

HOST_D4

HOST_D5

HOST_D6

HOST_D7

HOST_D0

HOST_D1

HOST_D2

HOST_D3

HOST_D4

HOST_D5

HOST_D6

HOST_D7

HOST_A0

HOST_A1

HOST_A2

HOST_A3

HOST_A4

HOST_A5

HOST_A6

HOST_A7

HOST_A10

HOST_A11

HOST_A12

HOST_A13

HOST_WE#

HOST_OE#

HOST_ACK

HOST_RD

#CS_FLASH_DG

POD_DET#

POD_DAT_DIR

CI_CD1_N

CI_CD2_N

CI_CE1_N

CI_WAIT_N

CI_IRQ_N

CI_RESET

HOST_BOOT_CS#

HOST_RD

HOST_D2

HOST_D3

HOST_A0

HOST_A2

HOST_A4

HOST_A5

HOST_A7

MUX_TSI_SYNC

MUX_TSI_VAL

MUX_TSI_CLK

MUX_TSI_D0

MUX_TSI_D1

MUX_TSI_D2

MUX_TSI_D3

MUX_TSI_D4

MUX_TSI_D5

MUX_TSI_D6

MUX_TSI_D7

POD_A4

POD_A5

POD_A6

POD_A7

POD_A8

POD_A9

POD_A14

HOST_A8

HOST_A9

HOST_A14

HOST_D8

HOST_D9

HOST_D10

HOST_D11

HOST_D12

HOST_D13

HOST_D14

HOST_D15

HOST_D8

HOST_D9

HOST_D10

HOST_D11

HOST_D12

HOST_D13

HOST_D14

HOST_D15

HOST_A15

HOST_A16

HOST_A17

HOST_A18

HOST_A19

HOST_A20

HOST_A21

HOST_A22

HOST_A23

HOST_A24

HOST_A15

HOST_A16

HOST_A17

HOST_A18

HOST_A8

HOST_A19

HOST_A9

HOST_A20

HOST_A21

HOST_A14

HOST_A22

HOST_A1

HOST_A2

HOST_A3

HOST_A4

HOST_A5

HOST_A6

HOST_A7

HOST_A10

HOST_A11

HOST_A12

HOST_A13

HOST_A23

HOST_A24

HOST_ACK

Flash_WP#

POD_DET#

HOST_A24

Flash_WP#

Flash_WP#

HOST_A1

HOST_A3

HOST_A6

HOST_A23

HOST_WE#

HOST_WE#

HOST_OE#

HOST_CS0#

HOST_BOOT_CS#

+3V3_A

+3V3_A

+3V3_A

+3V3_A

+3V3_A

+3V3_A

+3V3_A

CI_RESET

CI_CE1_N

CI_WAIT_N

PWR_/RESET

POD_A4

POD_A5

POD_A6

POD_A7

POD_A8

POD_A9

POD_A14

CI_CD1_N

CI_CD2_N

CI_IRQ_N

HOST_D[15..0]

HOST_A[24..0]

MUX_TSI_VAL

MUX_TSI_SYNC

MUX_TSI_CLK

POD_DET#

POD_DAT_DIR

#CS_FLASH_DG

MUX_TSI_D2

MUX_TSI_D1

MUX_TSI_D6

MUX_TSI_D5

MUX_TSI_D4

MUX_TSI_D3

MUX_TSI_D7

MUX_TSI_D0

HOST_WE#

HOST_OE#

HOST_CS0#

HOST_BOOT_CS#

BOOT STRAP SETTING

All location are from 181 to 220

BSTRAP_BOOT_MODE

BSTRAP_EXT_OSC

BSTRAP_16BIT_FLASH

BSTRAP_NAND_FLASH_EN

BSTRAP_PAGESIZE

BSTRAP_NAND_FLASH_DWIDTH

BSTRAP_NOR_FLASH_SEL

Bootstrap

Pin Name

POD_HOST_A0

POD_HOST_A1

POD_HOST_A2

Pins POD_HOST_A[1:0] indicate on chip

hardware the host interface configuration

to use after hard reset:

A1;A0 = 00 = Function test, vendor mode.

A1;A0 = 01 = Function test, vendor mode.

A1;A0 = 10 = Boot from FLASH

A1;A0 = 11 = Boot from IROM

Pin POD_HOST_A2 indicates:

0 = Internal osc

1 = External osc

Pin POD_HOST_A3 indicates type of

memory for external boot FLASH.

0 = 8-bit FLASH

1 = 16-bit FLASH

Pin PODREG_HOST_A4 indicates type of

memory for external boot FLASH.

0 = NOR FLASH

1 = NAND FLASH

Pin POD_IOWR_HOST_A5 indicates page

size for off chip NAND FLASH.

0 = Small page NAND FLASH

1 = Large page NAND FLASH

Pin POD_IORD_HOST_A6 indicates data

width for NAND FLASH (used by IROM

boot s/w only).

0 = 8-bit NAND FLASH

1 = 16-bit NAND FLASH

Pin HOST_A[7] selects whether parallel

NOR flash or SPI flash is used for boot

when BSTRAP_BOOT_MODE=10 (IROM

bypass). Ignored if

BSTRAP_BOOT_MODE != 10.

0 = boot from parallel NOR flash

1 = boot from SPI flash

POD_HOST_A3

POD_HOST_A4

POD_HOST_A5

POD_HOST_A6

POD_HOST_A7

Description

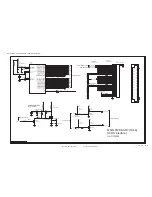

NOTE.

64 MBit FLASH : R203, R204, L26 OPEN

128 MBit FLASH : R204, L26 OPEN

256 MBit FLASH : L27 OPEN(P30 Series)

A24 setting default value "0" when STi7103 access flash

HOST WE# setting default value "1" when STi7103 access flash

R184

OPEN-103/1005

C183

104p/16V/1005

R186

C184

104p/16V/1005

R185

103/1005

R181

330/1005

R205

103/1005

R190

103/1005

R197

103/1005

R182

103/1005

R195

103/1005

R203

000/1005

R191

103/1005

TP181

PCB_TP08

1

R234

103/1005

C185

104p/16V/1005

R200

103/1005

R204

000/1005

R199

000/1005

U102C

FLI10620H

POD_DETEC_N

AD4

POD_DIR_N

AD5

POD_CE_1

AE4

POD_A4_CTX

AE3

POD_A5_ITX

AF3

POD_A6_ETX

AF2

POD_A7_QTX

AG2

POD_A8_CRX

AF1

POD_A9_DRX

AG1

POD_A14_MCLKO

W5

POD_VS2_MCLKO

W6

POD_BVD2_MOVAL

Y5

POD_BVD1_MOSTRT

Y4

POD_D15_MDO7

AB1

POD_D14_MDO6

AA1

POD_D13_MDO5

Y1

POD_D12_MDO4

AB2

POD_D11_MDO3

AA2

POD_D10_MDO2

Y2

POD_D9_MDO1

AA3

POD_D8_MDO0

Y3

POD_HOST_D0/SPI_SDI

AG7

POD_HOST_D1

AJ8

POD_HOST_D2

AG8

POD_HOST_D3

AE7

POD_HOST_D4

AH9

POD_HOST_D5

AF9

POD_HOST_D6

AJ10

POD_HOST_D7

AG10

HOST_D8

AF7

HOST_D9

AH8

HOST_D10

AE8

HOST_D11

AJ9

HOST_D12

AG9

HOST_D13

AE9

HOST_D14

AH10

HOST_D15

AF10

POD_WE_HOST_WR

AJ13

POD_OE_HOST_RD

AF8

HOST_ACK

AG3

HOST_DEV_CS2_N

AE5

HOST_DEV_CS1_N

AF4

HOST_DEV_CS0_N

AJ4

HOST_BOOT_CS_N

AG6

POD_HOST_A0

AJ15

POD_HOST_A1

AH15

POD_HOST_A2/SPI_SDO

AG15

POD_HOST_A3/SPI_CLK

AE14

POD_REG_HOST_A4

AF14

POD_IOWR_HOST_A5

AG14

POD_IORD_HOST_A6

AH14

HOST_A7

AJ14

HOST_A8

AE13

HOST_A9

AF12

POD_HOST_A10

AG12

POD_HOST_A11

AH12

POD_HOST_A12

AJ12

POD_HOST_A13

AE11

HOST_A14

AF11

HOST_A15

AG11

HOST_A16

AH11

HOST_A17

AE10

HOST_A18

AF13

HOST_A19

AG13

HOST_A20

AE12

HOST_A21

AD13

HOST_A22

AH13

HOST_A23

AJ11

HOST_A24

AD9

HOST_READY

AH5

POD_CD1

V5

POD_CD2

V4

POD_CE_2

W4

POD_WAIT_N

V3

POD_READY_IRQ_N

V2

POD_RESET

V1

OOB_CTX

W1

OOB_CRX

W2

OOB_DRX

W3

R187

103/1005

R192

OPEN-103/1005

L182

BLM18PG300SN1D

R198

OPEN-103/1005

R202

OPEN-103/1005

R193

330/1005

R196

OPEN-103/1005

R183

472/1005

R220

103/1005

R206

472/1005

U181

PC28F256P33BF/BGA

A1

A1

A2

B1

A3

C1

A4

D1

A5

D2

A6

A2

A7

C2

A8

A3

A9

B3

A10

C3

A11

D3

A12

C4

A13

A5

A14

B5

A15

C5

A16

D7

A17

D8

A18

A7

A19

B7

A20

C7

A21

C8

A22

A8

A23

G1

A24

H8

NC(A25)

B6

CE

B4

OE

F8

WE

G8

WP

C6

RFU5

B8

RFU4

E8

RFU3

F1

RFU2

G2

RFU1

H1

VPP

A4

VCC

A6

VCC

H3

VCCQ

D5

VCCQ

D6

VCCQ

G4

VSS

B2

VSS

H2

VSS

H4

VSS

H6

DQ0

F2

DQ1

E2

DQ2

G3

DQ3

E4

DQ4

E5

DQ5

G5

DQ6

G6

DQ7

H7

DQ8

E1

DQ9

E3

DQ10

F3

DQ11

F4

DQ12

F5

DQ13

H5

DQ14

G7

DQ15

E7

RST

D4

CLK

E6

ADV

F6

WAIT

F7

C182

106p/10V/2012

C181

104p/16V/1005

R217

103/1005

R194

103/1005

R188

OPEN-103/1005

R189

330/1005

R201

103/1005

MAIN PWB(9/46)

MAIN PWB(10/46)

MAIN PWB(9/46)

MAIN PWB(10/46)

MAIN PWB

(9/46),(24/46)

MAIN PWB(9/46),(45/46),(46/46)

MAIN PWB(45/46),(46/46)

MAIN PWB(45/46)

MAIN PWB(45/46)

MAIN PWB(6/46)

MAIN PWB(9/46),(46/46)

MAIN PWB(9/46)

MAIN PWB CIRCUIT DIAGRAM (8/46) [Flash and CI Interface]