2-20(No.YA707<Rev.001>)

(No.YA707<Rev.001>)2-19

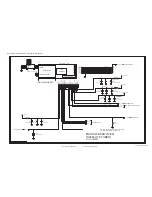

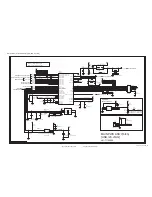

MAIN PWB ASS'Y(6/46)

[USB,I2C,JTAG]

HU-71100006

hb1_main_0612_4/48_0.0

5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

USB_D0-

UART0_RX

UART0_TX

UART1_TX

UART1_RX

UART0_TX

UART0_RX

DINT

TRST#

EJTAG_RST#

TDI

TDO

TMS

FLI_SCL_0

FLI_SDA_0

TCK

WP

NVRAM_WP

NVRAM_WP

FLI_SCL_0

FLI_SDA_0

FLI_SDA_1

FLI_SCL_1

+5V_USB

+5V

+1V2

+5V_USB

+3V3_A

+3V3_A

+3V3_A

+3V3_A

+3V3_A

+3V3_A

+3V3_A

+3V3_A

+3V3_A

+3V3_A

+5V

+5V

P_DIM

A_DIM

CI_PWR

LPM_RST_N

FLI_INT

PWR_/RESET

BLT_EN

FRC_/RST

FLI_SDA_0

FLI_SCL_0

FLI_SDA_1

FLI_SCL_1

UART1_RX

UART1_TX

UART0_RX

UART0_TX

EJTAG

All location are from 111 to 160

EEPROM

Address:0xA4/A5

UART0 : PC Display Debug message

UART1 : G-Probe application run at PC

Reset Threshole

: +3.08V

NVRAM_WP : H = Enable write

NVRAM_WP : L = Disable write

Active high

STi7103_UART

C129

100uF/16V/MVK/S

C116

104p/16V/1005

R126

102/1005

C112

OPEN-680p/50V/1005

C123

104p/16V/1005

C122

104p/16V/1005

R137

103/1005

R119

330/1005

R128

622/F/1005

R127

103/1005

R129

OPEN-472/1005

R111

OPEN-104/1005

R135

OPEN-472/1005

TP112

PCB_TP08

1

C119

105p/16V/1005

C126

5R0p/50V/1005

C125

5R0p/50V/1005

C120

104p/16V/1005

C127

106p/10V/2012

TP111

PCB_TP08

1

R124

OPEN-000

PR111

103*4/1005

1

8

2

7

3

6

4

5

R112

000/1005

R125

OPEN-200/1005

C114

270p/50V/1005

RV111

OPEN-AVRL161A1R1NTB

C113

270p/50V/1005

U111

OPEN-ASM811REUSF-T

GND

1

RESET

2

VCC

4

MR

3

R121

330/1005

C124

106p/10V/2012

L111

BLM18PG300SN1D

Q111

MMBT4401

1

23

2mm

JP113

OPEN-53014-0410

4

3

2

1

R133

OPEN-153/1005

U113

24LC256

A0

1

A1

2

A2

3

VSS

4

VCC

8

SCL

6

SDA

5

WP

7

R115

222/1005

R131

103/1005

R116

222/1005

R120

330/1005

R134

OPEN-153/1005

R138

103/1005

R139

000/1005

C121

104p/16V/1005

L113

ACM2012H-900

3

2

1

4

R113

222/1005

L114

BLM21PG600SN1D

Y111

19.6608MHZ/

20PF/SX-1/SMD

1

2

R132

103/1005

R118

330/1005

R136

OPEN-472/1005

JP111

OPEN-2110-DS14-G

1

3

5

7

9

11

13

14

12

10

8

6

4

2

RV112

OPEN-AVRL161A1R1NTB

R122

000/1005

R123

102/1005

JP112

KJA-UB-4-0004

VBUS

1

D-

2

D+

3

GND

4

1

2

3

4

SGND

5

SGND

6

C118

47uF/16V/MVK/S

TP113

PCB_TP08

1

R117

222/1005

R130

OPEN-472/1005

C115

200p/50V/1005

L112

BLM18PG300SN1D

U114

R5523N USB HIGH-SIDE POWER SWITCH

EN

1

GND

2

FLG

3

IN

4

OUT

5

C117

104p/16V/1005

C128

104p/16V/1005

U102G

FLI10620H

USBPHY_VRES

AG20

USB_FLAG

C29

USBPHY_PADM

AH20

USBPHY_PADP

AJ20

PWM0_GPIO4_/INT4

D13

PWM1_GPIO5_/INT5

C13

PWM2_GPIO6

B13

PWM3

A13

CLKOUT

E12

TESTMODE0

C27

TESTMODE1

C26

TRST

B26

TDO

A27

TDI

B27

TMS

A28

TCK

B28

EJ_RST_N

A29

EJ_DINT

B29

2WIRE_M0_SDA

F20

2WIRE_M0_SCL

E20

2WIRE_M1_SCL_UART2_RX

D20

2WIRE_M1_SDA_UART2_TX

D21

UART0_RXD

A19

UART0_TXD

B19

UART1_TXD

B20

UART1_RXD

A20

UART1_RTS

C20

UART1_CTS

C19

RESET_N

D23

REF_CLK

A22

XTAL_IN

A23

OBUFC_CLK

F21

DFSYNC_IN_OUT_GPIO8

E13

USB_GND

AD20

USB_AVDD33

AH19

USB_AVDD33

AF20

USB_GND

AF19

USB_GND

AJ19

USB_AVDD12

AE20

USB_AVDD33

AG19

USB_PWREN

C28

OTP_VDD33

A26

S111

OPEN-JTP1127WEM

1

2

3

4

R114

OPEN-104/1005

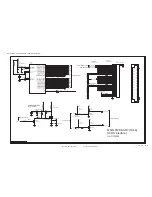

MAIN PWB(2/46),(26/46),(27/46)

MAIN PWB(36/46)

MAIN PWB(23/46)

MAIN PWB(3/46)

MAIN PWB(5/46),(17/46),(22/46),(40/46)

MAIN PWB(17/46)

MAIN PWB(10/46)

MAIN PWB(5/46)

MAIN PWB(5/46)

MAIN PWB(8/46)

MAIN PWB(3/46)

MAIN PWB CIRCUIT DIAGRAM (6/46) [USB,I2C,JTAG]