A

1

2

3

4

5

B

C

D

VOIC_LED

STIL_LED

VIDE_LED

CHRG_LED

ACES_LED

C1037

TALY_LED

FLSH_RST

REG_CS

DSP_RST

R1008

C1010

C1014

C1015

C1017

VPP

R1025

BUZZER

Q1001

Q1002

R1005

R1006

R1002

R1003

R1004

C1006

D1001

X1001

IC1006

IC1004

SCPU_SO

SCPU_SCK

C1013

C1007

SJIG_RST

C1012

BATT_L

C1011

ADP_L

R1048

R1001

R1011

R1039

C1016

SCPU_SI

R1049

C1020

R1054

R1055

R1052

R1053

IC1002

POFF_SW

LCD_OPEN

C1001

L1002

C1003

GND

REG_3.1V

R1015

AL_3.3V

L1001

C1005

IC1003

C1002

X1002

LIT_3V

C1008

R1007

R1027

C1004

C1021

R1051

R1050

C1019

C1018

V_BATT

I_MTR

VPP

AVDD

VDD

OSC2

OSC1

VSS

XI

XO

REG_DA

RTC_DA

MMOD

RESET

T_BATT

KEY_C

6.3V

2SC4617/QR/-X

DTC124EE-X

PDTC124EE-X

UN9212J-X

DA221-X

NAX0647-001X

SN74LV86ADGV-X

SN74LV32ADGV-X

S-80823CNNB-G-W

6.3V

VSS

VDD

SIO

CLK

CS

Xin

Xout

INTR

RS5C314-X

NAX0491-001X

10/

2.2K

0.01

0.01

0.01

470

10K

4.7K

150K

2.7K

18K

1

0.01

0.01

0.01

2.2K

100K

100K

470

0.01

470

0.01

100K

100K

1K

1K

10/

10

µ

0.1

470

10

µ

8p

0.1

0.01

47K

10K

0.1

0.1

100K

100K

0.1

0.1

REG_CLK

REG_DATA

TO CN208

TO REG

TO CN203, 208

TO CN207

TO CN208

TO CN209

TO ANA IF

TO CN203

TO CN209

TO TL202

TO CN208

TO CN203

TO AUDIO

TO CN203

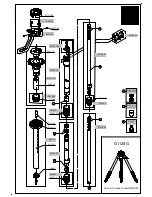

ANALOG(SUB CPU) SCHEMATIC DIAGRAM

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked (

) is not used.

2-17