Intel® Server Board S1200SP Family Technical Product Specification

100

Note: When performing this test, the probe clips and capacitors should be located close to the load.

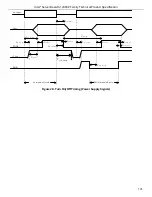

These are the timing requirements for the power supply operation. The output voltages must rise from 10%

to within regulation limits (T

vout_rise

) within 5 to 70ms. For 12VSB, it is allowed to rise from 1.0 to 25ms. All

outputs must rise monotonically. Table below shows the timing requirements for the power supply being

turned on and off via the AC input, with PSON held low and the PSON signal, with the AC input applied.

Table 59. Timing Requirements

Item

Description

MIN

MAX

UNITS

T

vout_rise

Output voltage rise time

5.0 *

70 *

ms

Tsb_on_delay Delay from AC being applied to

12VSBbeing within regulation.

1500

ms

T ac_on_delay Delay from AC being applied to all

output

voltages

being

within

regulation.

3000

ms

Tvout_holdup Time 12V output voltage stays within

regulation after loss of AC at 70% load.

13

ms

Tpwok_holdu

p

Delay from loss of AC to de-assertion

of PWOK

12

ms

Tpson_on_del

ay

Delay from PSON# active to output

voltages within regulation limits.

5

400

ms

T pson_pwok Delay from PSON# deactivate to

PWOK being de-asserted.

5

ms

Tpwok_on

Delay from output voltages within

regulation limits to PWOK asserted at

turn on.

100

500

ms

T pwok_off

Delay from PWOK de-asserted to

output voltages dropping out of

regulation limits.

1

ms

Tpwok_low

Duration of PWOK being in the de-

asserted state during an off/on cycle

using AC or the PSON signal.

100

ms

Tsb_vout

Delay from 12VSBbeing in regulation

to O/Ps being in regulation at AC turn

on.

50

1000

ms

T12VSB_hold

up

Time the 12VSBoutput voltage stays

within regulation after loss of AC.

70

ms

Note: The 12VSBoutput voltage rise time shall be from 1.0ms to 25ms

Summary of Contents for S1200SPL

Page 3: ......