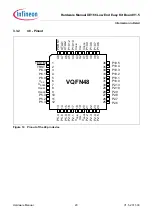

Hardware Manual XE166 Low End Easy Kit Board V1.5

Schematic

Hardware Manual

25

V1.5, 2011-03

5

Schematic

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

D

D

C

C

B

B

A

A

1

Infineon

Technologies

AG

ATV

MC

ACE

PDA

Am

Campeon

1-12

D-85579

Neubiberg

Tel.:

+49-89-234-0

3

29.09.2010

Number:

Date:

Sheet:

of

Easy

Kit

XC2XX

X

64/48/38

CPU

and

On

Board

IO's

1.1

Revision:

G:\Technical_Support\P

11\XC2XXX\EDA_DXP\Easy

Kit

XC2XXX\64_48_38

V1.X\Easy

Kit

xc2xxx

64_48_38

V1.1\Main.Sch

File:

R115

0R

1

2

Y101 8MHz

C103

18pF

C102

18pF

GND

GND

+5V

R131

0R

GND

R132 120R

R133

0R

R134

0R

CB102

100n

GND

R135 0R_opt

+5V

GND

R124 0R

+5V

R128 1K

CB101 100n

GND

C105 22µF/50V

GND

+5V

R109 0R

R110

0R

+5V

P2.0

P2.2

P2.3

P2.4

P2.5

P2

.6

P2

.7

/TESTM

XTAL1

XTAL2

/POR

ST

C101 1n

GND

P5

.0

P5

.1

P5

.2

P5

.3

P5.4

P5

.5

P5

.6

P5.7

P5.10

P5.11

P5.13

P5.15

P2

.13

P2

.5

P2

.3

P10.15

P10.13

P10.0

P10.1

P10.2

P10.3

P10.4

P10.5

P10.6

P10.7

/TRST

R101

1K5

R102

1K5

R103

1K5

R104

1K5

R105

1K5

R106

1K5

R107

1K5

R108

1K5

P2

.8

P2

.9

P2

.10

P2

.11

P2

.12

P6

.3

P2.1

D101

LY

T67K

D102

LY

T67K

D103

LY

T67K

D104

LY

T67K

D105

LY

T67K

D106

LY

T67K

D107

LY

T67K

D108

LY

T67K

R111

47K

GND

R114

100R

1

3

2

R113

10K

C104 100n

VAGND

P5

.0

VAGND

VAREF

1

3

2

4

X105

LI

N

GND

VBAT

R116 opt

R126

0R

R125

0R

R130

0R

R129

0R

/TRST

P5.9

P5.8

P10.7

P10.6

P10.5 P10.4 P10.3 P10.2 P10.1 P10.0

1 3 5 7 9 11 13 15

2 4 6 8 10 12 14 16

X102

C

PUCON2_opt

HOLD

7

WP

3

VCC

8

CS

1

GND

4

SO

2

SCK

6

SI

5

U107

AT25128N-10SI2.7

CB104 100n

R144 10K

R145 10K

R146 10K

GND

+5V

P2

.8

P2

.4

P2

.10

P2

.7

TRST

3

XTAL1

62

XTAL2

61

PORST

63

TESTM

2

P5

.0

11

P2.0

25

P2.1

26

P2.2

29

P2.3

30

P2.4

31

P2.5

32

P5.4

17

P2

.7

35

P2

.9

37

P2

.10

38

P2

.8

36

P6

.0

7

P6

.1

6

P6

.3

4

P10.0

43

P10.1

44

P10.2

45

P10.3

46

P10.4

47

P10.5

48

P10.6

49

P10.7

50

P10.8

51

P10.9

52

P10.10

58

P10.11

59

P10.12

60

P10.13

53

P10.14

54

P10.15

55

ESR0

64

VDDI1

57

VDDPB

8

VDDPB

28

VDDPB

56

GND

1

VDDPB

42

GND

33

VDDI1

27

VAGND

10

VAREF

9

P6

.2

5

P5

.1

12

P5

.2

13

P5

.3

14

P5

.5

15

P5

.6

16

P5.7

18

P5.8

19

P5.9

20

P5.10

21

P5.11

22

P5.13

23

P5.15

24

P2

.11

39

P2

.13

41

P2

.12

40

P2

.6

34

U101 XC2XXX

LE

64

PI

N

P10.15

P10.14

P10.13

P10.12

P10.11

P10.10

P10.9

P10.8

ESR0

GND

2

RXD

4

CANH

7

TXD

1

VCC

3

CANL

6

STB

8

SPL

IT

5

U105

T

L

E6251DS

1

X108 SP

L

IT_CAN0_opt

1 2 3 4

8 7 6 5

1

S101

CONFI

G

P1

0.12

/TRST

P2

.9

R121

2K8

R122

0R

R127

10K

+5V

R119

470R

R120

470R

1 3 5 7 9

2 4 6 8 10

X106

CAN0

R140

0R

R141

0R

R142

0R

R143

0R

PORT[2..10]

GND

1

3

2

D109

BAT54-04

R112

10K

1

3

2

X107

I2C_opt

P10.1

P10.2

GND

TRST

36

PORST

34

TESTM

35

P5

.0

3

P2

.0

8

P2

.3

11

P2

.4

12

P2

.5

13

P2

.6

14

P2

.7

15

P2

.9

17

P2

.8

16

P6

.0

38

P6

.1

37

P10.0

19

P10.1

20

P10.2

21

P10.3

22

P10.4

23

P10.5

24

P10.6

25

P10.7

26

P10.8

27

P10.9

28

P10.10

32

P10.12

33

VDDI1

31

VDDPB

10

VDDPB

29

GND

30

VAGND

2

VAREF

1

P5

.2

4

P5

.3

5

P5

.4

6

P5

.8

7

GND

9

P2

.10

18

U103

XC2XXX

ULE

38

PI

N

TRST

2

XTAL1

47

XTAL2

46

PORST

48

TESTM

1

P5

.0

10

P2.0

16

P2.1

17

P2.2

21

P2.3

22

P2.4

23

P2.5

24

P2

.6

25

P2

.8

27

P2

.9

28

P2

.7

26

P6

.0

5

P6

.1

4

P6

.3

3

P10.0

31

P10.1

32

P10.2

33

P10.3

34

P10.4

35

P10.5

36

P10.6

37

P10.7

38

P10.8

39

P10.9

40

P10.10

44

P10.12

45

VDDI1

43

VDDPB

7

VDDPB

20

VDDPB

41

VDDI1

18

VAGND

9

VAREF

8

P5

.2

11

P5

.3

12

P5.4

13

P5.8

14

P5.9

15

GND

6

GND

19

GND

42

P2

.10

29

P2

.13

30

U102 XC2XXX

LE_ULE

48

PI

N

1 3 5 7 9 11 13 15

2 4 6 8 10 12 14 16

X103

C

PUCON3_opt

1 3 5 7 9 11 13 15

2 4 6 8 10 12 14 16

X101

C

PUCON1_opt

1 3 5 7 9 11 13 15

2 4 6 8 10 12 14 16

X104

C

PUCON4_opt

VDDPB

VDDI1

VDDPB

XTAL1

XTAL2

GND

VDDPB VAREF VAGND

VDDI1

VDDPB

GND

+5V

P6

.0

P6

.1

P6

.2

/TESTM

ESR0

P2.0

P2.2

P2.3

P2.4

P2.5

P2

.6

/TESTM

/POR

ST

P5

.0

P5

.2

P5

.3

P2

.8

P2

.9

P2

.10

P6

.3

P2.1

/TRST

P5.9

P5.8

P10.7

P10.6

P10.5 P10.4 P10.3 P10.2 P10.1 P10.0

P10.12

P10.10

P10.9

P10.8

VDDI1

VDDPB

XTAL1

XTAL2

GND

VDDPB VAREF VAGND

VDDI1

VDDPB

P6

.0

P6

.1

GND

GND

GND

GND

+5V

R136 1K

_opt

R137 1K

_opt

+5V

+5V

VDD

3

A

L

ERT

5

GND

2

SDA

6

SCL

4

AS

1

U106

AD7414ART_opt

R138 opt

R139 opt

GND

+5V

CB103 100n_opt

GND

+5V

VDDPB

VAREF VAGND

VDDPB

VDDI1

GND

GND

P5

.3

P6

.1

P2

.3

P2

.5

P2

.8

P2

.10

P10.5

P10.3

P10.1

/TRST

P10.7

P10.9

P5

.0

P5

.2

P5

.4

P6

.0

P2

.0

P2

.4

P2

.6

P5

.8

P2

.7

P2

.9

P10.6

P10.4

P10.2

P10.0

/TESTM /PORST P10.12 P10.10

P10.8

CB109 100n

R148

0R

R123

0R

+5V

GND

VAREF

VAGND

CB114 100n

VAGND

VAGND

CB111 470n

CB115 470n

VDDI1

CB110 470n

GND

CB105 100n

CB106 100n

CB107 100n

CB108 100n

GND

CB113 100n

CB112 100n

R147

0R

+5V

PLEASE

NOTE:

ONLY

ONE

CPU

(U101,

U102

OR

U103)

IS

ASSEMBLED

PORT[2..10]

EN

2

IN

H

8

BUS

6

TXD

4

WK

3

RXD

1

VS

7

GND

5

U104

T

L

E7259

GND

ADBUS5

R150

0R

R149

0R

P10.6

P10.0

P5.4

P2

.7

P2

.13

/TESTM

P5

.0

P5

.1

P5

.2

P5

.3

P5

.5

P5

.6

P6

.3

/TRST

GND

VDDPB

VAREF

VAGND

P6

.0

P6

.1

P6

.2

P2

.0

P2

.2

P2

.3

P2

.4

P2

.5

P5

.4

P5

.7

P5

.10

P5.11

P5

.13

P5.15 P2

.1

P5

.9

P5

.8

VDDI1

VDDPB

P2

.6

P2

.7

P2

.13

P2

.8

P2

.9

P2

.10

P2

.11

P2.12

P10.5

P10.4

P10.3

P10.2

P10.1

P10.0

VDDPB

GND

/PORST

P10.7

P10.6

P10.15

P10.14

P10.13

P10.12

P10.11

P10.10

P10.9

P10.8

ESR0

VDDI1

VDDPB

XTAL1

XTAL2

R149

AND

R150

ARE

ASSEMBLED

ONLY

WITH

XC2XX

X

ULE

R125

AND

R126

ARE

ASSEMBLED

ONLY

WITH

XC2XX

X

LE

ONLY

WITH

XC2XX

X

LE