EM78P312N

8-Bit Microcontroller

Product Specification

(V1.0) 10.03.2006

•

23

(This specification is subject to change without further notice)

5.4 CPU Operation Mode

Registers for CPU Operation Mode

R_BANK

Address

NAME

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3 Bit 2 Bit 1 Bit 0

Bank 0

0X05

SCR

0 PS2

PS1

PS0 0 1

SIS REM

−

−

−

−

R/W

R/W

R/W

−

−

R/W R/W

* R_BANK: Register Bank (Bits 7, 6 of R3), R/W: Read/Write

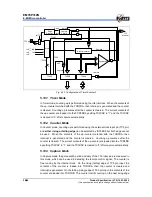

Normal Mode

CPU : Operating

Fosc: Oscillates

Reset Occurs

SIS=0 + SLEP

Sleep Mode

CPU : Halts

Fosc: Stops

Idle Mode

CPU : Halts

Fosc: Oscillates

Interrupt

SIS=1 + SLEP

/SLEEP Pin Input

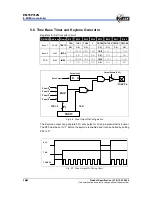

Fig. 5-4 Operation Mode and Switching

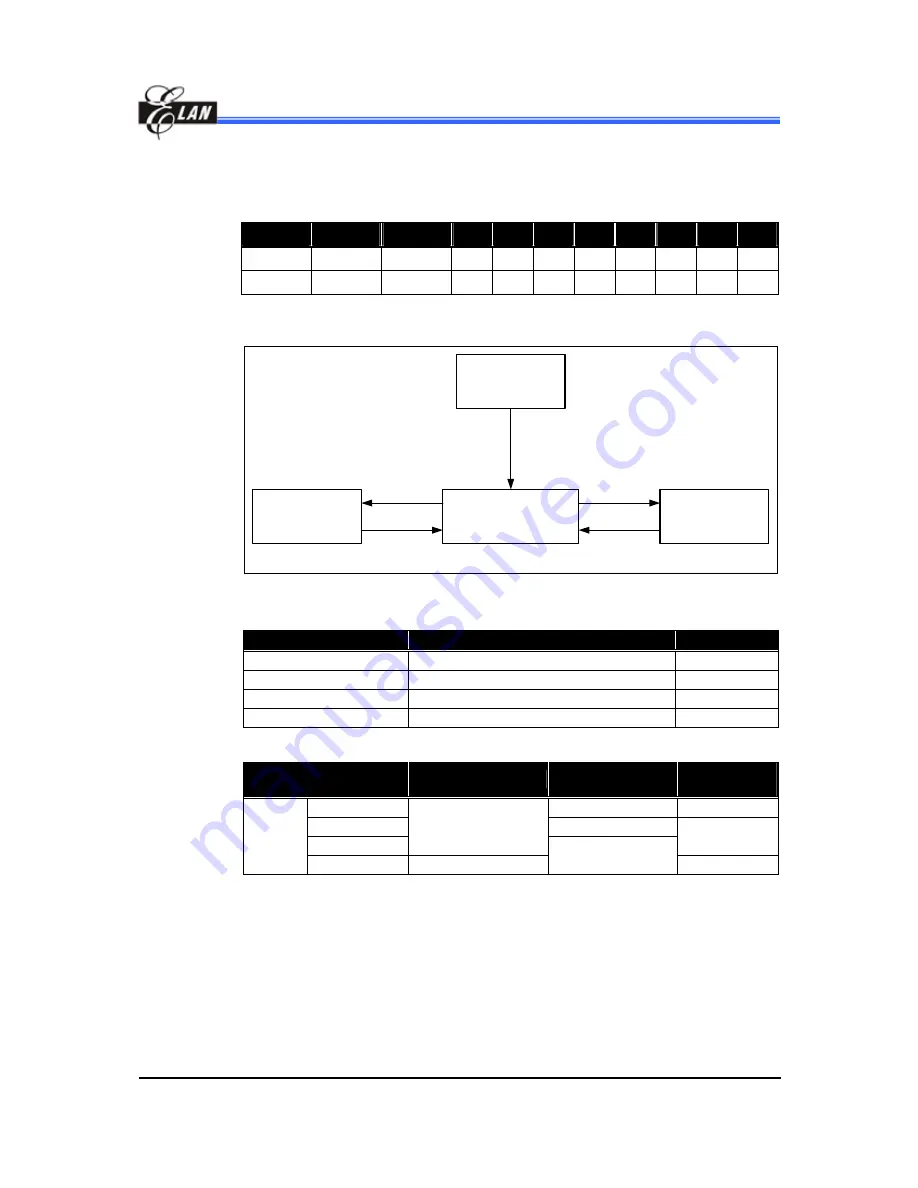

Table 2. Mode Switching Control

Mode Switch

Switch Method

Note

Normal

Æ

Sleep

Set SIS = 1, execute SLEP instruction

−

Sleep

Æ

Normal

/SLEEP pin wake up

−

Normal

Æ

Idle

Set SIS = 0, execute SLEP instruction

−

Idle

Æ

Normal

Interrupt

−

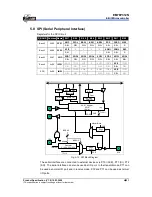

Table 3. Operation Mode

Operation Mode

Frequency

CPU Code

On-chip

Peripherals

Reset Reset

Reset

Normal Fosc

Idle

Turn on

Fosc

Signal

Clock

Sleep Turn

off

Halt

Halt

In Normal mode, the CPU core and on-chip peripherals operate in oscillator frequency.

In Idle mode, the CPU core halts, but the on-chip peripheral and oscillator circuit remain

active. Idle mode is released to Normal mode by any interrupt source. If the ENI

instruction is set, an interrupt will be serviced first followed by executing the next

instruction which is after the Idle mode is released and the interrupt service is finished.

If the ENI instruction is not set, the next instruction will be executed which is after the

Idle mode start instruction. Idle mode can also be released by setting the /RESET pin

to low and executing a reset operation.