Beijing Huahuan Electronics Co., Ltd

Huahuan

- 6 - TDMUX-16 User Manual V1.2

2.2 Function Description

The core of H0FL-ETHMUX V16 is the TDM/Packet processing unit. It

truncates E1 data stream, putting the data into Ethernet packet with or without IP

headers. The packets are passed to the Ethernet switch unit via MII interface, and

are sent out adaptive the uplink ports. Ethernet data from two local data port are

also sent out through the uplink ports, but with lower priority than those packets

containing E1 data.

In the reverse direction, packets from the uplink ports are sorted at the switch

unit. All but E1 packets are passed to the local data ports. The packets containing

E1 data are sent to the TDM/Packet processing unit for reassembling the original

data stream, and recovering the E1 clock which is the key element of the device.

Very sophisticated algorithm is used to ensure that the reconstructed clock will

meet the stringent requirement of TDM applications. The most important

parameters are jitter, wander, and signal delay.

The control unit interfaces with the user through console port so that various

operational parameters can be modified.

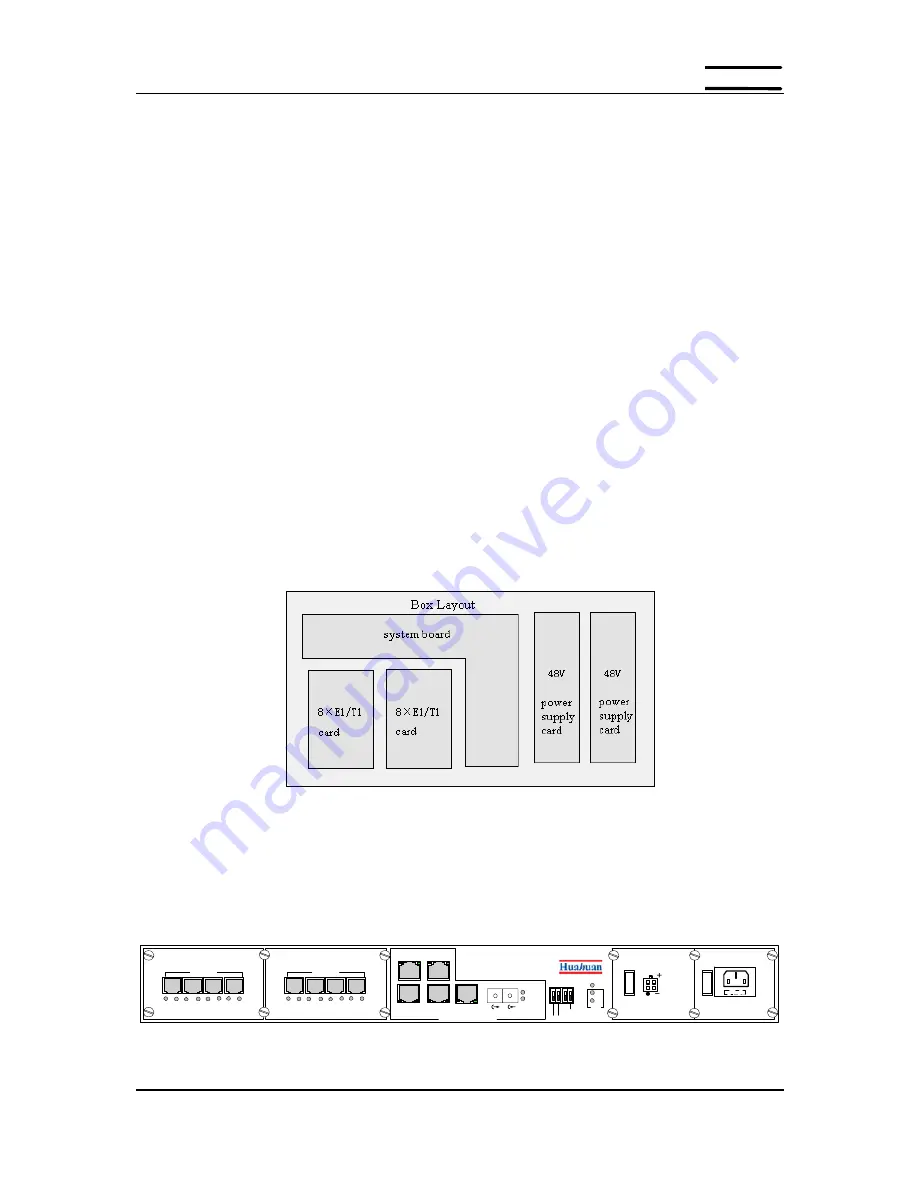

2.3 Structure

H0FL-ETHMUX V16 adopt standard 1U box, which is composed by system

board, power supply card and E1/T1 card. System structure is shown as 2.3-1:

2.3-1 H0FL-ETHMUX V16 system structure

2.4 Front panel

2.4.1

Front panel and Rear panel

H0FL-ETHMUX V16 is shown in Fig. 2.4-1. and Fig 2.4-2.

1 2 3

4 5 6 7 8

E1/T1

LINK

SPD

1

LINK

SPD

2

LINK

SPD

3

LINK4 SPD LINK5 SPD

6

LINK

OLOS

10/ 100/ 1000 ETHERNET

LED_ MODE

TMP_IP

SYS

1

2

PWR

FAIL

I

0

1 2 3

4 5 6 7 8

E1/T1

H0FL-EthMux V16

PWR01

DC 48V

I

0

PWR02

AC 100-240V 50-60Hz 1A

Fig. 2.4-1 Front panel of H0FL-ETHMUX V16